日志

Foundry ESD方案“万事大吉”? ——芯片可靠性挑战与ESD防护:从代工厂方案到定制化治本之道

| |

在现今这个高度数码化的时代,芯片已经是电子产品的中心。不管是在智能手机,汽车电子,或者是工控系统中,它的可靠度都决定着一个产品的工作稳定度和工作时间。以汽车行业为例,自动驾驶芯片若因可靠性问题失效,可能导致严重的安全事故。这样,芯片就需要符合工业规范,如AEC-Q100(汽车电子)或JEDEC(消费电子)。

研究表明,近40%的芯片早期失效与静电放电(ESD)和电气过载(EOS)有关。这些瞬时高压事件可能在制造、封装、测试甚至终端使用阶段发生,最好的结果,就是出现故障,甚至是永久的损伤。

芯片可靠性大致受以下几种因素影响:1. 制造缺陷:工艺波动、金属层短路/开路、栅氧击穿等;2. 环境应力:温度循环(Thermal Cycling)、机械振动、湿度腐蚀;3. 电气应力:ESD、EOS、热载流子效应(HCI)、负偏置温度不稳定性(NBTI);4. 设计缺陷:信号完整性不足、电源噪声、闩锁效应(Latch-up)。在集成电路的生产,封装,测试及使用过程中, ESD是最普遍的瞬间高电压。其脉冲电压可达数千伏(如人体放电模型HBM的2kV),远超芯片工作电压。因此ESD是芯片可靠性的主要威胁。

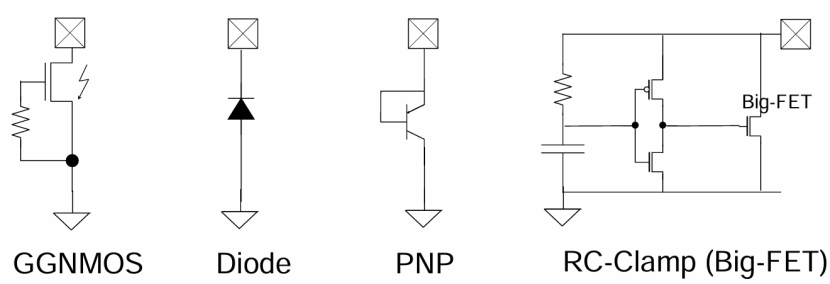

业界一般将静电保护措施划分为三个层次:1. 系统级:PCB上添加TVS二极管、磁珠等外围保护元件。2. 封装级:采用ESD友好材料(如导电胶)、优化引脚布局。3. 芯片级(最关键):在芯片内部集成ESD保护器件,分为被动防护(二极管、SCR、GGNMOS等泄放路径)和主动防护(动态触发电路,如RC检测+功率管)。大部分芯片设计公司,尤其初创企业和中小企业会选择代工厂提供的免费通用ESD器件来保护芯片。尽管代工厂(如TSMC、SMIC)提供标准化的ESD器件库,但是,这些常用的解决方法很难达到对高性能集成电路的要求。

图1 代工厂提供的ESD器件

代工厂(如TSMC、SMIC)通常提供标准化ESD器件库,其优缺点如下:

ESD器件 | 利 | 弊 |

二极管阵列 | 响应快、面积小 | 钳位能力弱,需多级防护 |

GGNMOS | 兼容CMOS工艺,设计灵活 | 触发电压高,热失效风险大 |

SCR结构 | 高电流泄放能力 | 易引发闩锁效应 |

RC触发电源钳位 | 动态响应精准 | 占用面积大,增加设计复杂度 |

表1 代工厂(如TSMC、SMIC)通常提供标准化ESD器件库

更深层次的问题:1. 通用性与定制化的矛盾:代工厂方案为通用设计,难以适配高频、高压等特殊场景(如5G射频或SiC功率芯片)。2. 黑盒化风险:部分ESD器件的仿真模型不透明,造成设计确认和实测之间的巨大差异。3. 隐性成本高:标准ESD器件可能占用较大面积,增加芯片成本;若防护不足,还需重新流片,延误产品上市时间。

Foundry ESD方案作为通用技术方案,可能不一定适合具体芯片设计要求,但要彻底解决ESD问题,就需结合芯片应用场景定制防护方案:

1. 协同设计:

- 与Foundry合作优化ESD器件的工艺参数(如Deep N-well隔离)。

- 在I/O、电源轨、敏感电路(如PLL)周围布局差异化保护结构。

2. 动态防护技术:

- 采用瞬态检测电路(Transient Detector)快速触发泄放路径。

- 例如:某5G射频芯片通过"二极管+主动MOS"组合将ESD耐受能力提升至8kV。

3. 先进工艺适配:

- 在FinFET工艺中设计低电容ESD器件以减少信号损耗。

- 针对SiC功率模块开发高压SCR结构(耐压>1.2kV)。

代工厂的标准化ESD方案为芯片提供了基础保护,但在高性能、高可靠性应用中,定制化的设计是最基本的方法。通过协同设计,动态保护,以及高级的制程调整,可以极大地提高集成电路的抗静电性能,降低失效风险。未来,结合DTCO和AI技术,ESD防护将迈向更智能、更高效的新阶段。

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网