日志

芯片面积杀手?ESD防护模块占比优化50%的三大法则

| ||

ESD防护模块确实是现代芯片,特别是大规模SoC芯片中不可忽视的“面积杀手”。优化ESD防护模块面积是一个极具挑战性但通过正确方法可以实现的目标。其核心三大法则可以归纳为:

法则一:工艺与设计的协同优化

它要求芯片设计团队与晶圆厂从项目伊始就紧密合作,充分利用先进工艺的特性,不要将ESD防护视为一个独立的、后期添加的模块,而是将其作为整个芯片I/O和工艺设计的一部分。

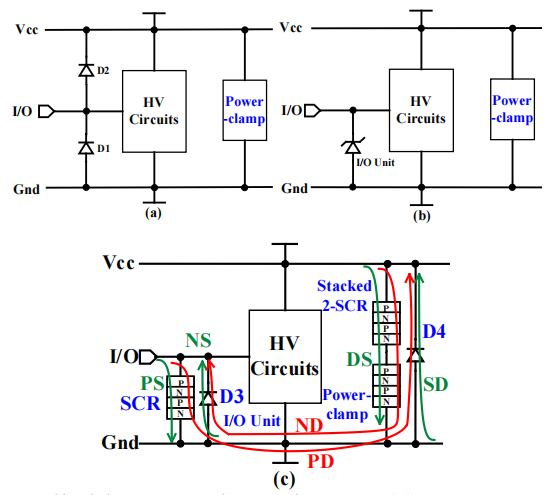

图1:全芯片保护方案:(a) 常规ESD保护方案 (b) 典型高压ESD保护方案

(c) 本项工作中提出的新型高压ESD保护方案。

具体方法是采用固有ESD性能更优的工艺,或者利用器件本身的寄生结构,让核心电路器件自身承担一部分ESD防护功能,从而减少甚至省去旁边独立的ESD器件。同时还要做到设计规则检查与ESD规则融合,与Foundry合作,制定更智能的ESD设计规则,尽可能缩小ESD器件的间距和尺寸。这样可以从源头实现面积大幅缩减。

法则二:分布式与主次防护结构优化

核心思想是摒弃为每个Pad都配备一个庞大、独立的ESD防护单元的传统“一刀切”模式,侧重于整个ESD防护网络的架构设计,采用高效、共享的分级防护网络。

具体方法是首先要做分级防护。主级防护是在芯片的电源轨之间放置一个(或少数几个)大型、高效、但面积相对较大的中央泄放单元,在ESD事件发生时,为整个芯片提供一条强大的全局泄放路径。同时有次级防护,即在每个I/O Pad旁边,只放置一个极小尺寸的本地触发单元,从而灵敏地检测ESD事件,并迅速触发那个强大的中央泄放单元。其次是电源钳位共享,这是分级防护的核心。一个强大的中央Power Clamp可以被所有I/O单元共享。当任意一个I/O对地发生ESD冲击时,电流路径都会经过电源轨,从而激活这个共享的Power Clamp进行泄放,避免在每个I/O单元都设计一个全尺寸的泄放器件。最后是要做分布式设计,可以采用多个分布式的中等规模Power Clamp,服务于不同区域的I/O,以优化泄放路径的电阻和响应速度。

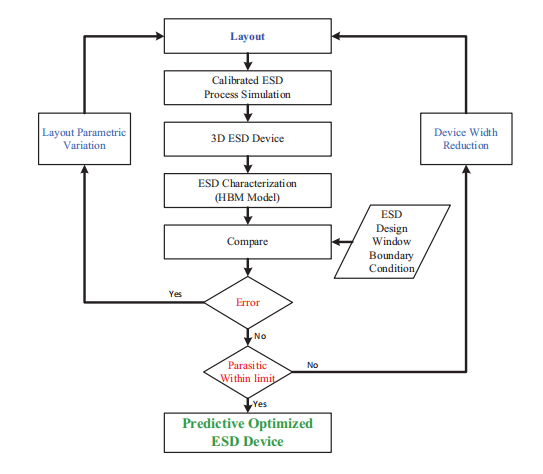

图2:ESD优化流程路径的流程图

同时,针对具体的产品设计和全芯片ESD架构,IO/电压的ESD单元有不同的工作分工要求,其面积可以进一步压缩,从而优化降低全芯片的版图面积。

此方法将ESD面积成本从“每个Pad支付”转变为“整个芯片支付一次”,极大降低了I/O数量众多时的总面积开销,是实现50%优化的核心架构手段。

法则三:智能布局与模块共享

其核心思想是最大化利用布局中的“闲置”区域,并让多个电路模块共享同一块物理面积。优化物理层,“挤”出面积。

具体方法是可以仔细分析I/O Cell的内部结构,将二极管可以巧妙地布局在I/O驱动管的源漏区旁边,或者利用I/O Cell内部的隔离环作为ESD的一部分,避免为ESD单独开辟新的有源区。也可以通过特殊的布局技巧,让ESD二极管的扩散区与I/O输出级的MOS管扩散区物理上相连或交错,消除隔离间距,节省大量的“无用”面积。在先进封装中,ESD结构可以直接制作在Pad的金属球下方,几乎不占用额外的面积。也可以为不同类型的I/O设计高度优化的标准ESD单元库,在整个芯片中复用,避免重复设计。

此法则通过“精打细算”的物理设计,通常能带来10%-25%的面积优化,是前两个法则的重要补充。

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网