日志

分频后的jitter会有变化吗?

热度 10| ||

在之前的文章中,写到过,分频后的相位噪声会下降20log(N)dB,有读者提出问题,jitter会发生变化吗?如何变化。

既然讲到jitter,那么首先需要理解一下jitter的定义。

jitter的定义

相位噪声是对一个信号的频率评价,而jitter是对一个信号的时域评价。

jitter实际上是表示一个信号的周期波动大不大的程度。而在统计理论中,评价数据的波动性,常用极差(最大值-最小值),方差和标准差表示。而jitter使用的是标准差和极差。

其中标准差就是均值 (RMS) jitter,而极差就是峰峰值(peak to peak) jitter

而jitter的测量也有不同的方式。

①时间间隔误差 Time Interval Error(TIE)

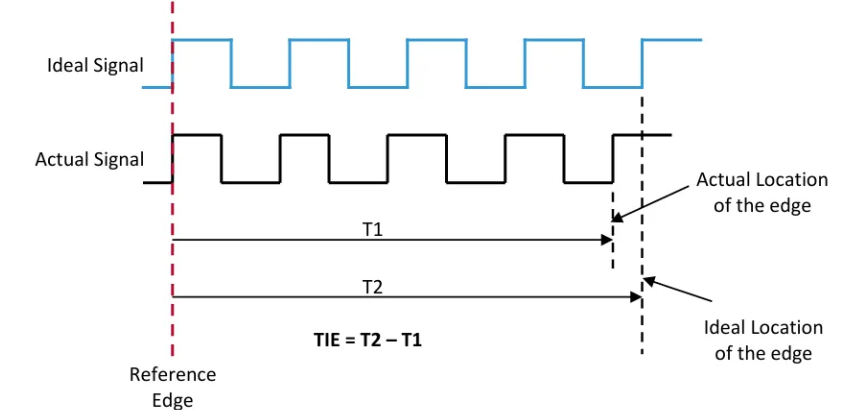

确定好一个开始的参考边沿,然后求第n个边沿与理想的边沿的时间差,如下图,TIE的求取方法。

TIE jitter又称phase jitter。

②周期抖动 PJ (Period Jitter)

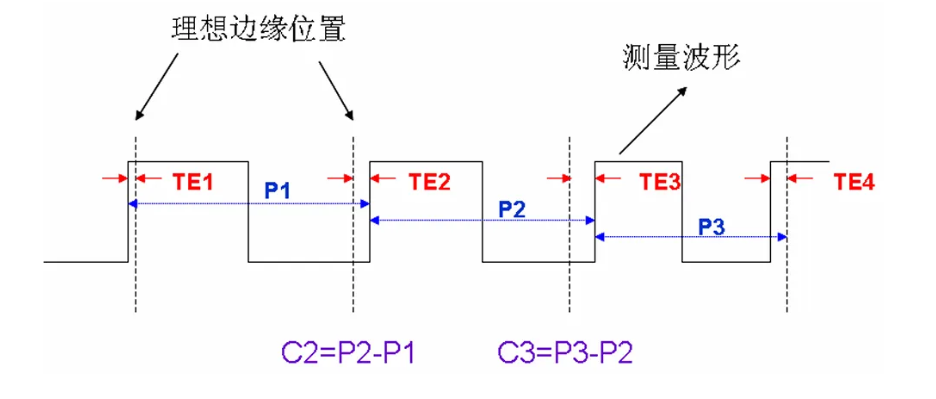

period jitter是求每个周期与理想周期的差值。如下图所示,P1-理想周期就是period jitter的差值。

③相邻周期间CCJ (Cycle to Cycle Jitter)

cycle to cycle jitter是指相邻两个周期的差值。如上图中的C2和C3都是CCJ。

回到问题,N分频后,jitter变化了吗

在pll中,常用counter来实现分频,以下分析都是基于counter实现分频的。

①TIE

假设未分频的信号第m个上升沿的TIE为TIE(m),那么N分频后的TIE则是TIE(Nm)。

相当于分频后的TIE是未分频的TIE的一个子集。

那么RMS会改变吗?不会。还是一样的。

②period jitter

假设未分频的信号的标准差为σ,第k个周期的周期为T[k]=T + j[k],其中T是理想周期,j[k]是第k个周期的period jitter。

那么N分频后的周期为(以N=2为例)

T[k] + T[k+1] = T + j[k] + T + j[k+1]

那么,2分频后,period jitter变为 j[k]+ j[k+1],由于j[k]和j[k+1]服从高斯分布,且不相关,

因此,2分频的方差为 VAR( j[k] )+ VAR( j[k+1] ) = 2 σ²

标准差为√2σ,扩展到N分频,为√Nσ

period jitter变差,会影响什么?

period jitter变差,会影响时序电路的时序裕量,在建立时间检查和保持时间检查时,需要更足的裕量。

如何解决问题呢?

可以使用retiming,详细可以看我以前的文章,有哪些retiming的方法。

参考文献

①Texas Instruments.正确理解时钟器件的抖动性能。

②SiTime. Clock jitter Definitions and Measurement Methods

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网