日志

sdm的dither有什么用?

热度 11| |||

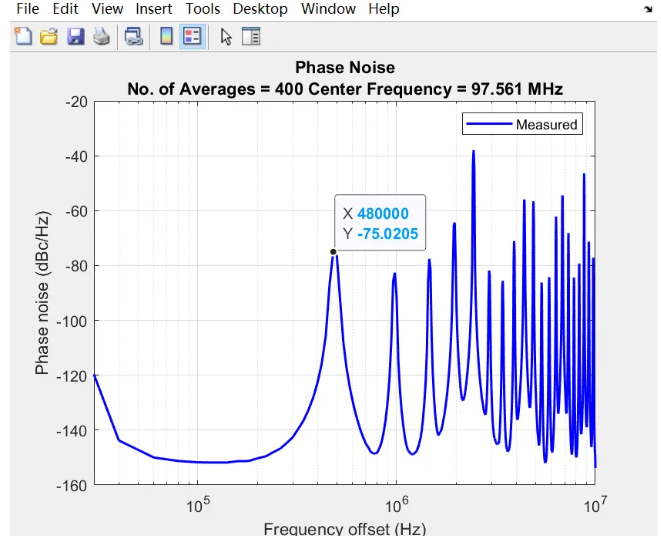

现象:sdm+分频器出现了spur

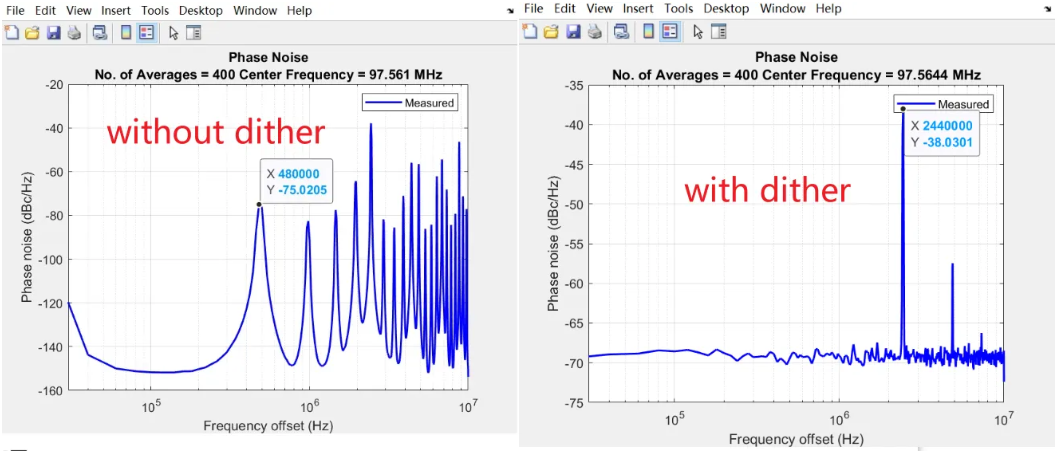

我们上次搭建了mash 1 1 1的simulink结构。在此基础上,加上一个vco和分频器级联仿真,发现,分频器的输出相位噪声会有spur。这个是2GHz的20.5分频,分频后频率为97.5609756MHz,可以看到在480kHz左右有一个-75dBc的spur,并且还有其他spur。这是为什么呢?我们先看看不同分频比的输出相位噪声是如何的。

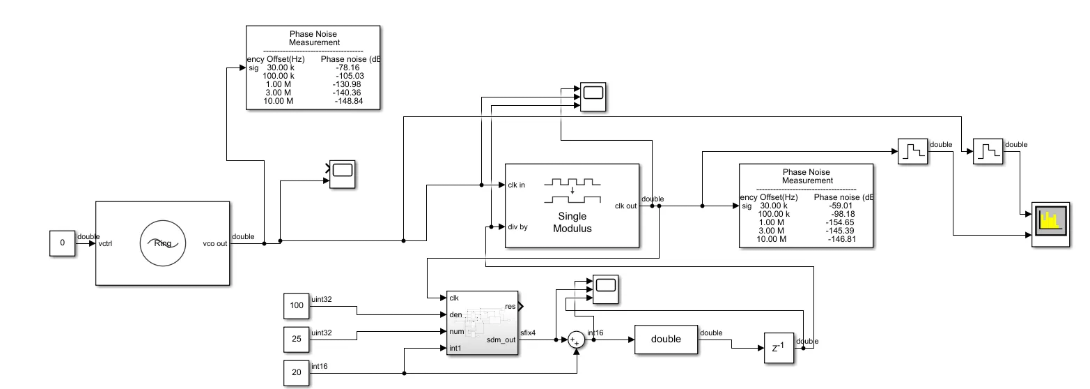

下面是我的级联仿真图

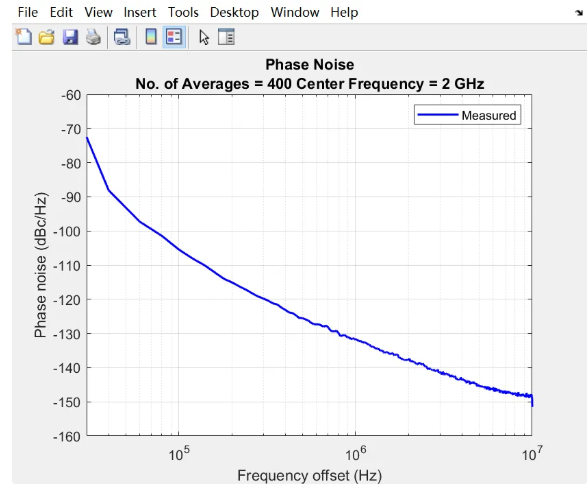

设置vco为2GHz,噪声-90dBc@30kHz,-106dBc@100kHz,-132dBc@1MHz,-152dBc@10MHz,VCO的相位噪声仿真图如下

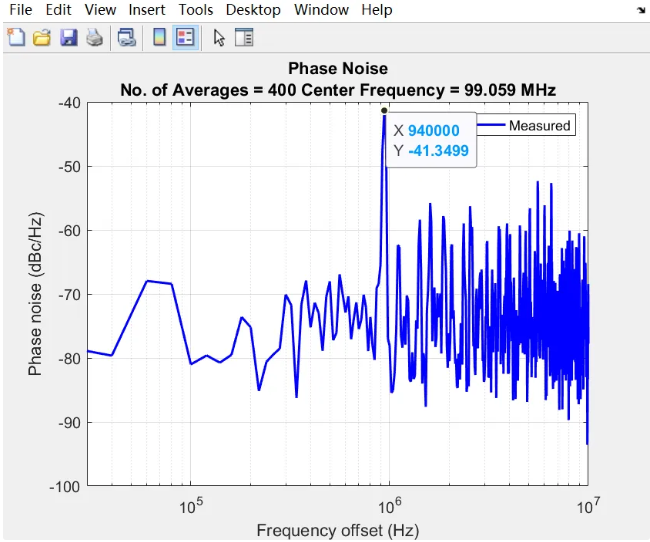

设置另一个分频,20.19分频,理论分频后频率为99.0589401MHz,下图为开环的分频器+sdm相位噪声仿真图,可以看到在940kHz左右有一个-41dBc的spur

从中可以发现,无论是0.5这样周期序列比较短的小数分频,还是0.19这样周期序列长的小数分频,都会有spur。

还有就是,小数是0.19的sdm输出序列比0.5的长,而周期序列长的信号,spur会更少,噪声更平坦,但相应的,底噪也抬升了。

出现spur的原因是什么呢?

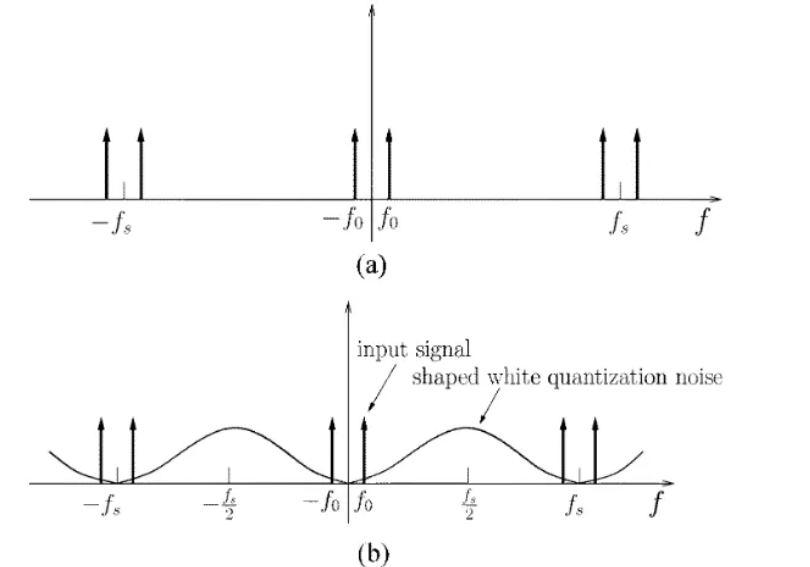

本质上,sdm输出的序列还是具有周期性的,导致sdm的噪声体现不是一个白噪声,而是具有一些谐波。频域上的表现如下图。

如果我们不想要这些谐波,有什么办法可以消除呢?

我们首先想到的是滤波,但是,一个PLL的分频比有很多种情况,你很难用一个滤波器去滤除所有的情况的spur。而且在PLL环路中,大部分的环路滤波器的带宽不会太低,还是会有spur在带宽内。

那有没有什么其他办法呢,我们其实最后想要的是一个平坦的噪声,于是我们想到可不可以将sdm的输出序列的周期变得更长呢,如果可以长到无穷大,那就是非周期信号了,就不会有spur了。

如何增加序列的周期呢?

既然sdm的输出有一个周期,那我可以和另一个信号相加,可以得到一个新的信号。这个新的信号的周期是什么呢?是这两个周期的最小公倍数。这其实是一个简单的定理,假设两信号周期分别是T1,T2,如果T1,T2都是有理数,那么相加之后还是周期信号,周期为T1和T2的最小公倍数。如果T1和T2是无理数,那相加之后不再是周期信号。

那么,怎么让新的信号周期尽可能长呢?那就是相加的信号周期尽可能长,什么信号周期很长,随机信号,但是从电路实现的角度看,产生一个伪随机的信号是最实际的,所以dither常用的是伪随机序列生成器。常见的有线性反馈移位寄存器(LFSR),这个也是dither常用的方法。或者读者有其他方法可以告诉我。

另外一个问题,sdm的这个随机信号在哪里相加呢,简单划分的话,有三个选项,输入,输出,或sdm里面,首先在sdm里面加会非常复杂,需要重新对sdm的结构进行分析,可能还会破坏sdm的稳定性,暂时不考虑这个方向,也有相关论文是在sdm里面加的,比如HK-MASH结构,SP-MASH,有兴趣的可以看看文后的参考文献,已经有相关论文发表了。那sdm的输出呢,看起来很不错,但会影响分频比的范围,在PLL中,分频比范围大了,对PFD的鉴相范围也会增加。那么就考虑在sdm的输入加,因此现在大多数dither都是在sdm的输入增加的。

LFSR是什么?怎么把LFSR加到sdm中

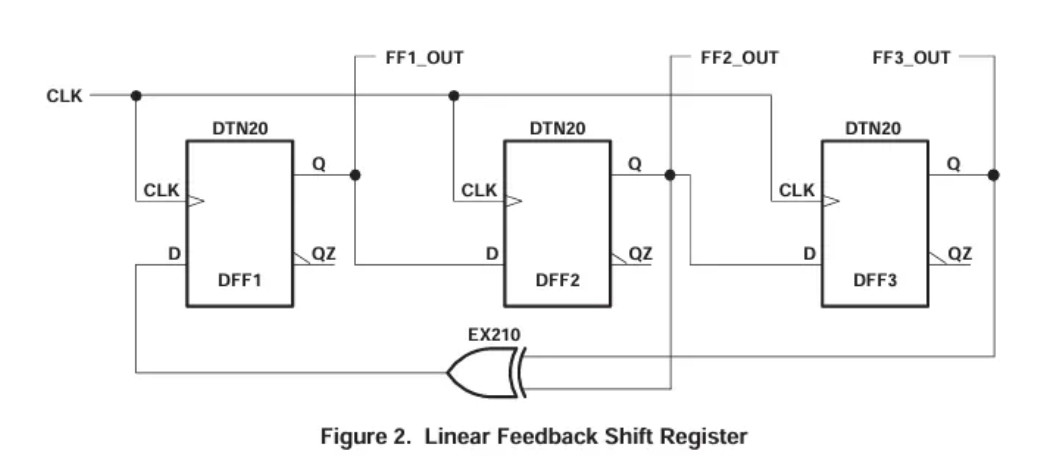

下面是TI的文章what‘s an LFSR的图

可以清晰看到,其实LFSR是就是几个触发器和一个异或门组成的时序电路。这几个触发器会输出一串序列。

说是伪随机序列,但还是会有周期的,周期是2^n-1,如果取其中1bit,那么输出的bit是2^n-1为周期的序列。但是LFSR的输出是0或者1,因此LFSR的平均值绝对是一个大于0的数,直接加在sdm的输入相当于有一个dc,会改变sdm的输入,也就是最后的分频比会变化。

如何处理?

常规思路有几种:①把LFSR的输出变为均值为0的;②加在分频比LSB,但是需要保证分频比误差在我们接受范围之内。大家可自行按照自己的需要修改。

增加了LFSR的SDM输出会怎么样呢?下面是我的simulink仿真图,大家可以看到,增加了dither的分频器输出,spur减少了,但底噪增加了。因此可以根据PLL的带宽设计适合自己PLL的dither信号。

sdm的初始值

看论文后发现,sdm的初始值其实也会影响sdm的输出序列,这个是我之前未曾想到的。为什么初始值也会影响sdm的输出序列呢?

大家都知道,MASH 1 1 1是有三个counter的,假如你初始值的counter不是0呢,你的输出序列是不是会发生改变,大家可以看论文②中的一个仿真图,图中IC1,IC2,IC3分别是三个counter的初始值,也就是复位值。当IC1=1,IC2=IC3=0时,明显比IC1=IC2=IC3=0的情况的supr少了很多,一个小小的修改就能让SDM的性能提高。

有一个有用的结论是,在MASH 1 1 1中,第一个counter的初始值是奇数,会更大化sdm的输出序列周期

总结

其实总结下来,我们发现,最终影响小数分频的spur就是sdm输出序列的周期,如果sdm输出序列的周期越长,那spur就越小。

主要影响sdm输出序列的周期有三个因素:①初始值;②SDM的结构;③输入。

为了将PLL的spur减小,那么你必须考虑这几个综合因素。在最差的输入情况下,spur也保证在能接受的范围内。

sdm的设计还是比较多需要注意的,在PLL和AD/DA中的应用也会有所差别,还是有最新的论文在关注这方面,这个方面的研究还是大有可为。

论文和simulink模型可在我的公众号gh_c29cca7839c6自取,主页也有二维码,后续模型和论文都会不定时更新,有兴趣可以关注一下。欢迎大家交流

文献

①TI. what‘s an LFSR

②TCAS Ⅰ2007(HK-MASH SDM). Maximum Sequence Length MASH Digital Delta-Sigma Modulator

③TCAS Ⅰ2010(SP-MASH SDM). spur-Free MASH Delta-Sigma Modulation

④TCASⅡ2018. Influence of LFSR Dither on the Periods of MASH Digital Delta-Sigma Modulator

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网