日志

为芯片“穿新衣”的陷阱:先进封装下的静电暗流!

| ||

在集成电路产业中,我们常说“芯片设计是大脑,制造是心脏,而封装则是骨骼与皮肤”。封装为内部脆弱芯片提供保护、供电、散热,并与外部电路建立电气连接和机械支撑的“铠甲”与“桥梁”。然而,在这个精密的“穿衣”过程中,一个看不见的杀手——静电放电(ESD)——始终如影随形。

1970s-1980s,以双列直插封装(DIP) 为代表,通过引线框架连接,采用穿孔式安装。结构简单,但密度低,频率特性差;1980s-1990s,小外形封装(SOP)、四侧引脚扁平封装(QFP) 成为主流;1990s-2000s, 球栅阵列封装(BGA) 是革命性的进步。它将引脚从封装体四周变为底部的焊球阵列,极大地增加了I/O数量,并改善了电气性能;2000s-至今,封装的角色从“保护”转变为“性能增强”。晶圆级封装(WLP)、扇出型晶圆级封装(Fan-Out WLP)、2.5D/3D封装 等技术成为前沿,它实现了超短互联、超高密度和异质集成。

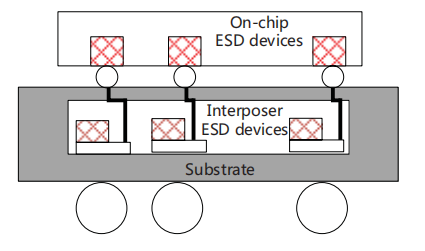

图1:芯片与中介层/基板的协同设计图

ESD失效的根本原理是瞬间的高压(数百至数千伏)和强电流在极短时间内(纳秒级)通过芯片内部电路,造成介质击穿(栅氧层烧毁)或热损伤(金属互连线熔断)。在封装厂(Assembly House)的各个环节,如晶圆减薄、切割、拾放、引线键合、塑封、测试等,芯片都会存在多种ESD威胁,封装形式越先进,其ESD风险往往越复杂。

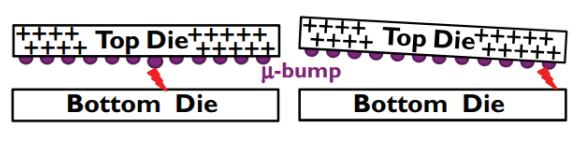

在QFP/BGA等引线键合类封装中,键合机的陶瓷吸嘴、环氧树脂底座等在高速运动中与材料摩擦会产生大量静电荷。当带有静电的吸嘴或夹具接近芯片的焊盘(Bond Pad)时,可能发生带电模型(CDM)ESD事件。在WLP/Fan-Out等晶圆级和重布线层封装中,在封装前的整个晶圆处理过程中,晶圆背面与塑料载具或金属导轨的摩擦会产生静电荷。由于WLP的I/O焊球(Solder Ball)直接通过再分布层(RDL)与芯片相连,整个晶圆表面都成为ESD敏感点,充电器件模型(CDM)风险极高,这是WLP封装面临的最大ESD挑战,晶圆本身可能成为一个巨大的充电载体。在2.5D/3D封装与SiP中,SiP将多个来自不同供应商的芯片集成在一起。一颗芯片可能在封装前已遭受潜在的ESD损伤(“暗伤”)。

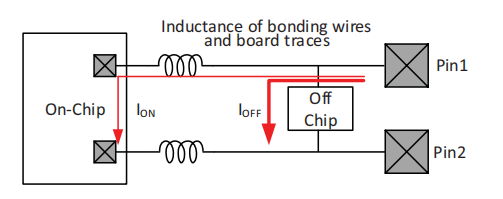

图2:CDM模式的局部静电放电

应对封装过程中的ESD风险,需要一个系统性的“设计-工艺-管理”综合方案。在芯片设计端,需要针对HBM和CDM的不同特性,设计鲁棒性高、响应速度快、且不影响芯片性能(如不增加过多电容)的集成高效的片上ESD保护电路(如GGNMOS、SCR、二极管等)。在封装工艺与环境端,封装厂必须建立符合ANSI/ESD S20.20标准的体系,全面实施ESD防护项目(ESDP)。

图3:片上器件与片外器件协同设计的基本原则

IC封装的演进,在带来性能飞跃的同时,也使得ESD防护的战场从二维走向三维,从外部走向内部。对于封装厂和芯片设计公司而言,理解不同封装技术下独特的ESD风险机理,是制定有效ESD防护策略的前提。通过在芯片设计源头植入鲁棒的保护方案,并在封装制程中执行严格的ESD控制体系,才能让这个“看不见的杀手”无处遁形。

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网