日志

明明加了 dither,为什么PLL 的 spur 却还是不降?

热度 13| |

之前有读者提问,自己的芯片测试出来,加了dither的sdm,输出序列完全没有spur,但是PLL输出还是会有spur,这是为什么?

我是认为,CPPLL中CP或者其他电路存在非线性,然后导致出现spur,但读者认为即便有非线性,最多让带内的噪声升高,为什么会出现spur呢。那具体是什么样呢?

我们其实可以简单的验证一下这个问题。

非线性分析方法

首先,这是一个非线性电路,所以常用的信号与系统在这个时候失效了,不能采用S域或Z域的系统函数去分析,那如何进行分析呢?

我们直接取SDM的输出序列求功率谱。

①验证白噪声经过非线性系统后功率谱变化

这里假设非线性系统的函数为y=0.8x+0.2x²+0.4x³

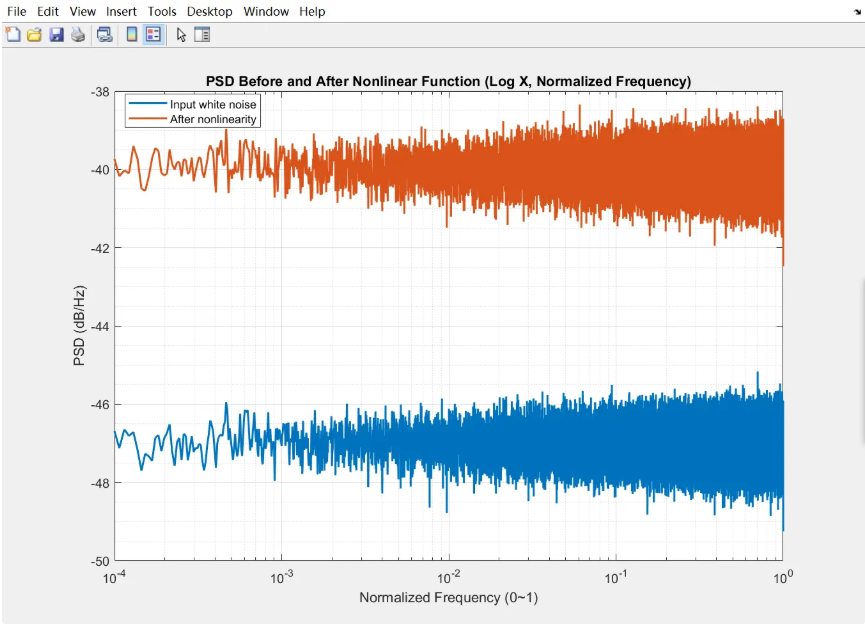

从下面的仿真图可以看成,白噪声在经过一个上面定义的非线性系统后,噪底提升了大概5-6dB,好像经过非线性系统,噪声会恶化,但不会形成spur。

那会不会是整形导致的问题呢?我们可以将白噪声整形一下再对比。

②白噪声三阶整形后功率谱变化

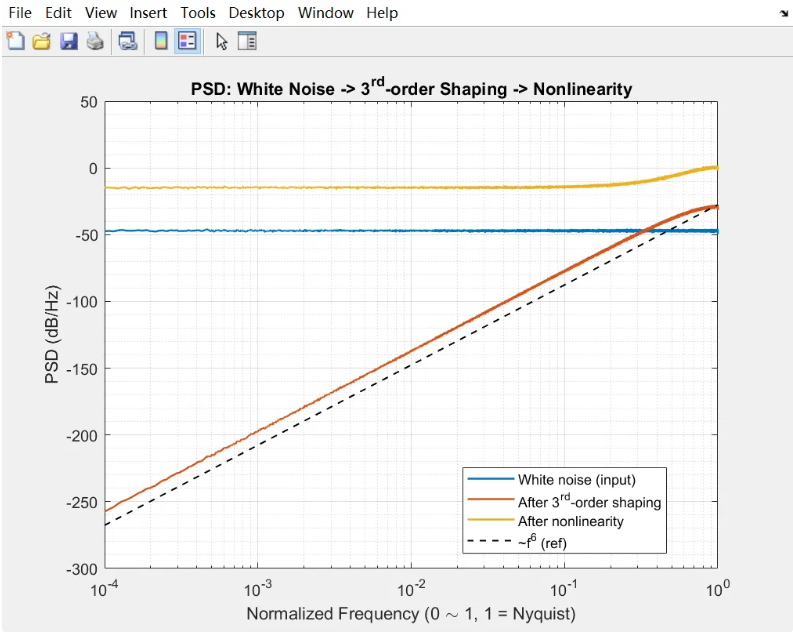

我们将白噪声经过一个系统函数为h[n]=(1−z−1)3,然后再经过非线性系统y=0.8x+0.2x²+0.4x³

从下图可以看到,经过三阶整形的序列,再经过非线性系统,噪声也抬高了,但是没有spur。

白噪声整形也没有出现spur,那再最终验证一下SDM的序列

③加dither后的SDM序列,经过非线性函数后功率谱变化

加dither的方式是在sdm输出添加

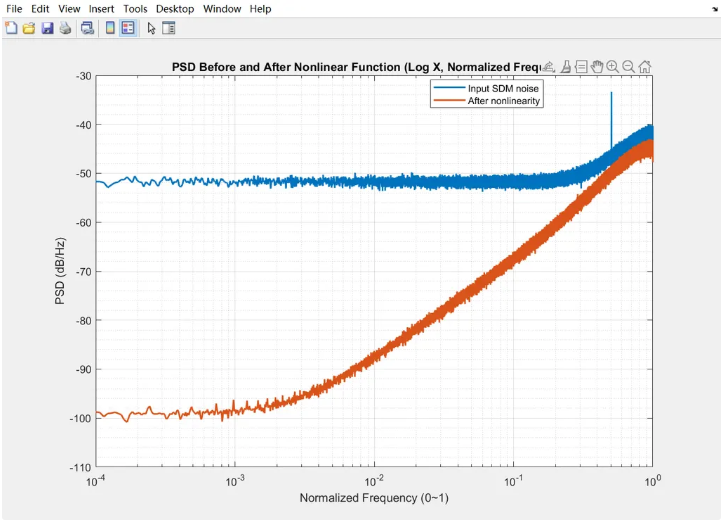

从下图可以看到输入的SDM三阶整形,没有spur,但是经过非线性函数后,出现了spur

以上的简单的验证,虽然不能证明白噪声经过非线性函数后不会出现spur,但可以知道的是即便SDM的序列没有spur,经过非线性函数后依旧会存在spur。

这是为什么呢,其实即便是加了dither的SDM,也存在最大周期。文献①中就证明过,MASH 1-1-1结构的SDM下,模为M,初始调节为奇数,一阶dither周期为Ld的情况下,SDM输出序列的周期是2MLd。举个例子,当M=225且由24bit的线性反馈移位寄存器生成的伪随机二进制序列时,周期为2MLd=10^15。

那如何去预测可能出现的spur和幅度呢。

预测小数spur幅度的方法

方法来自于文献②。

主要思想是通过统计的方法去实现。文章将SDM的量化误差分开,分为有周期的部分,和没有周期的部分,然后通过求期望的方法,求有周期部分导致的spur的大小和幅度,剩下的就是无规律部分产生的底噪了。

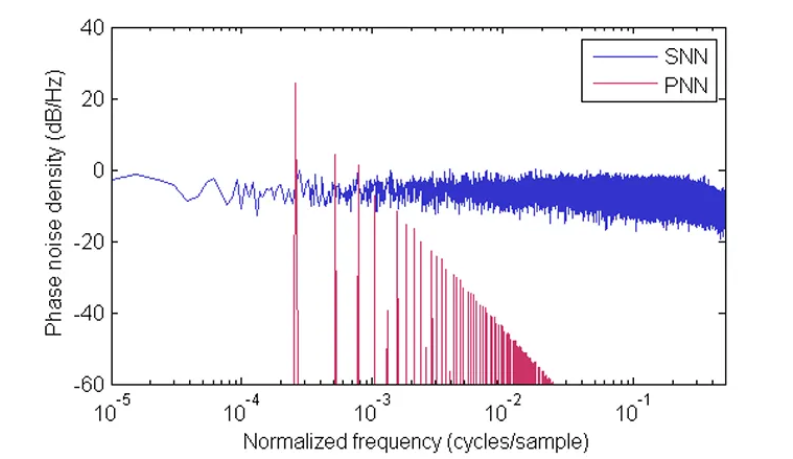

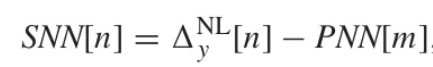

下图就是文献②中分割开的两部分,SNN为底噪,PNN为spur,可以看到,大部分spur会被底噪淹没,只有三个会出现在底噪上方。

具体的方法如下,不过还是建议精读一下文章。

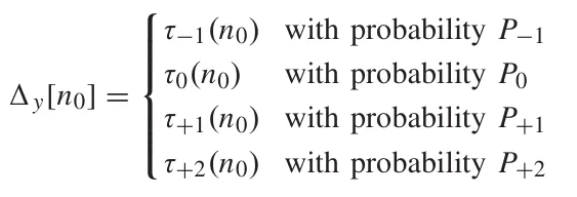

首先,文章将SDM中有规律的量化误差(由于加了dither,可以将量化误差分为两部分,一部分是有规律的,一部分是无规律的)进行分类,将其分为四类,τk(k =−1,0,+1,+2),然后这四个分类会有不同的概率,如下图所示

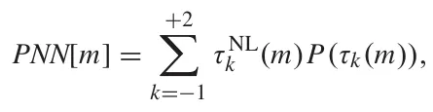

τk经过非线性函数后命名为τk_NL。那么这部分有规律的量化误差经过非线性系统后的序列就变成期望(概率乘以值)了。

而SDM的序列经过非线性系统后的底噪就用总的序列减去有规律的部分

文章还验证了CPPLL中常见的四种非线性,并预测spur位置和底噪,spur预测效果不错,但底噪还需要经过一个滑动平均滤波器才比较准确。下图为模拟CP的失配幅度为10%的spur预测图。可以看到,预测的幅度还是比较准的。

参考文献

①TCASⅡ2017.Influence of initial conditions on the fundamental periods of LFSR-dither MASH digital delta-sigma modulators

②TCASⅠ2019.Prediction of Phase Noise and Spurs in a Nonlinear Fractional-N Frequency Synthesizer

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网