日志

Layout中ESD,SAB层次覆盖住I/O的驱动级MOS是否降低其驱动强度?

| |

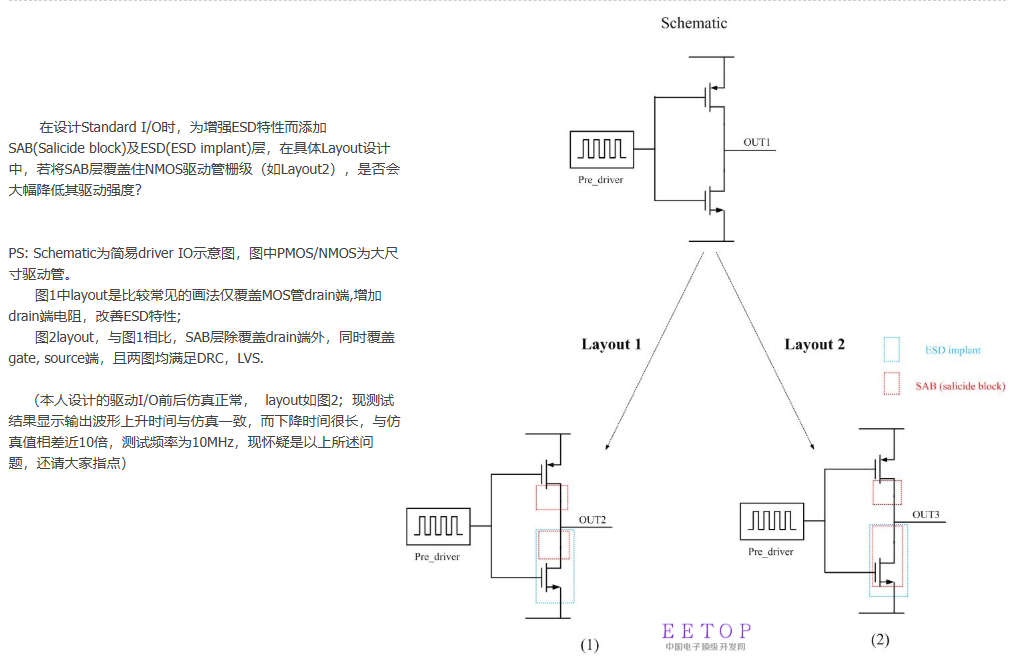

图二NMOS gate上覆盖SAB,相当于在栅极加了一个电阻,NMOS管响应时间增加,仿真相差10倍 ,看来去硅化这个电阻影响不小。

从PDK 中电阻模型来看,silicide/un_silicide ploy电阻,其方阻相差20倍左右。

前仿真无法cover住图2中 由于SAB drain端引入的电阻,gate端引入电阻。

后仿真与前仿真几乎一致,无明显差异, 且图1与图2 的后仿真结果一致,说明提取寄生参数无法corver 整个版图信息。

如果SAB只覆盖drain端以及gate的一小部分,会对驱动有影响吗?

如果仅仅考虑source端的SAB电阻,其电阻值只有10欧姆左右,不至于对驱动强度有10倍于仿真的区别。

是否是gate端被全部覆盖SAB层而导致的呢?那么其中的机理是什么?

SALICIDE这一层一般用在高值电阻与ESD器件上,即多晶硅块区域没有覆盖在上面,添加了SAB层的器件的区域电阻值就会抬高,可以看成是一个薄的高值注入层,为增大单位面积POLY电阻阻值和ESD的耐压等特性作出了贡献,但是如果加在了驱动管子的上面会对管子的VTH有影响,因为加大了BODY电阻,仿真响应时间也会延长

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网