日志

有关于smic018BCD工艺的几个疑问

| |

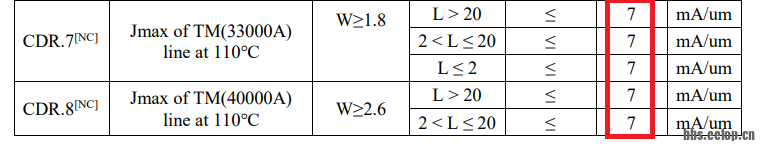

疑问1:为何33K和40K不同厚度的顶层金属,在DC时过流能力都是7mA/um;而在AC和IPeak时,过流能力有较大差异?

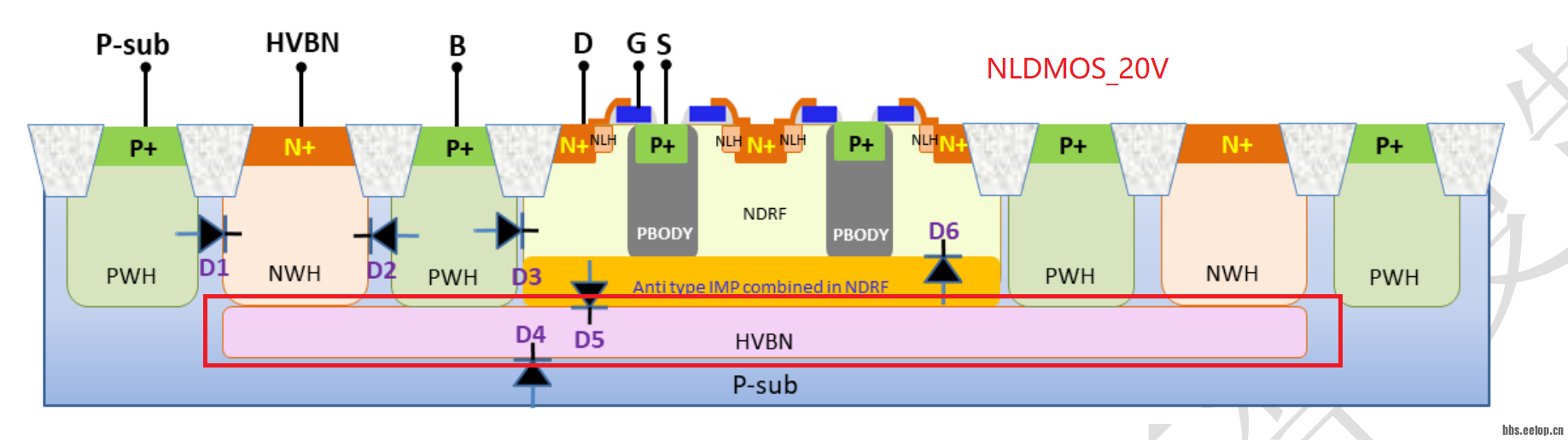

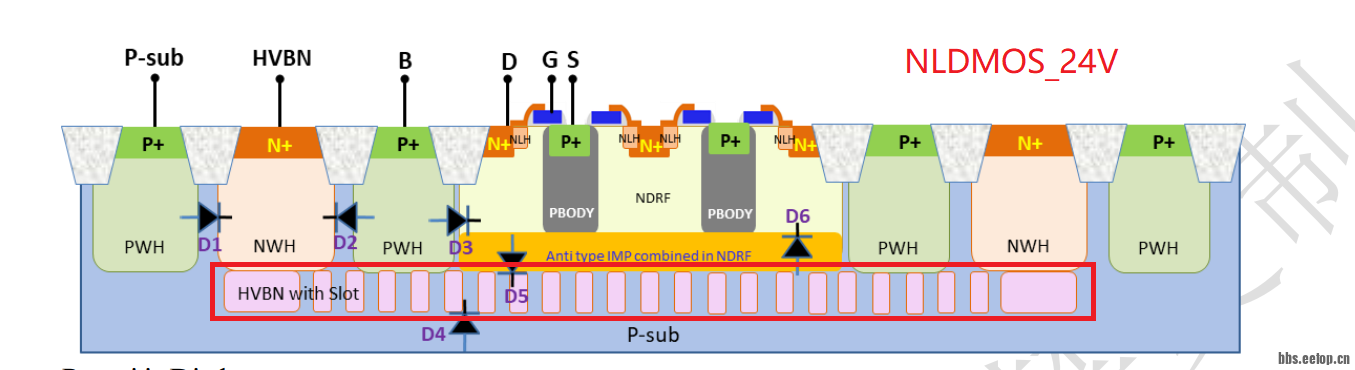

疑问2:大于20V的NLDMOS的NBL为什么会有Slot?不知道在工艺上有什么特殊操作和考量?

DC

20V 24V

芯片制造过程中有多次热退火,热退火会让离子进一步扩散,深埋层HVBN经多次的热退火再扩散最终形成均匀N型埋层,浓度也会比没Slot的低,以此提高耐压。

不是的吧,HVBN开孔能降低HVBN浓度,后面多道工序都涉及到退火,HVBN注入的离子肯定会重新分布的,应该会连上;

开孔是为了节约一层光罩,不然要一个低浓度HVBN,一个高浓度HVBN两层光照,工序也多了;

降低浓度是为了提高耗尽区宽度来提高耐压,所以只在高压的HVBN上有SLOT开孔。

都不是很严谨的解答:

1.过流能力那里40K厚度我就直接按照10mA/um算了,一般来说没问题,真功率管上的数据还是要靠R3d类似的软件去跑一下电流密度。

2.NBL是会扩散的,挖slot应该是为了控制浓度,在做jdv的时候,NBL这一层会往里缩很多,猜测就是统一的操作,来达到对应iso对应sub的耐压

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网