日志

AI在IC Layout 设计中的应用与CustomCompiler的集成

| |||

目前想要做一个对logic cell的快速布局优化的功能,类似对stdcell的auto placement。但又想参考电路上的布局进行优化。CustomCompiler中place like schematic 对模拟模块可以很好的参考布局。对logic cell 无法精确控制到像数字工具那样place in row。所以像完成这种场景的功能。

开始之前先介绍一个算法“粒子群优化PSO算法”:这个算法的灵感是鸟群觅食的行为。宏观上来看是可以借鉴这个算法个体向集体中心靠拢的思想。总归还是一种空间布局优化的场景。

还是使用AI来辅助开发,AI在生成Tcl/Python的代码质量非常高。(Custom Compiler 使用Tcl 和Python 为接口方便二次开发)所生成的代码只需要把参数接口对应好就可以直接在cc上运行。给工具的二次开发提供了便利。

后续待集成到Custom Compiler 看对实际cell操作摆放效果如何,当前先在开发的GUI显示。

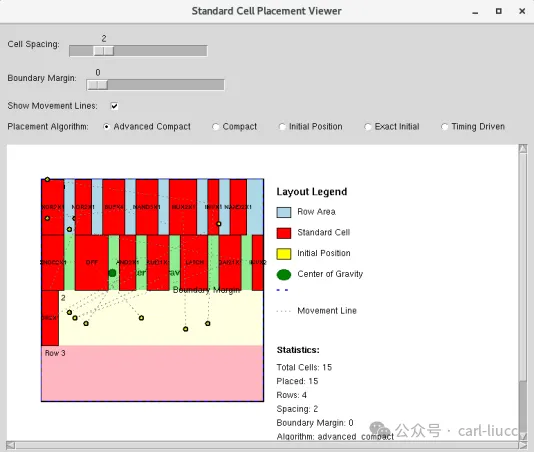

如下是用DS帮做的算法。使用TK搭出来的简单GUI演示图。模拟在版图中的小数字模块standcell 的摆放情况。

这个版本算是调整cell的space控制density的摆放,上图中黄点是初始位置,我们可以看成是schematic中对应各器件的symbol位置。虚线是指示当前摆放到的位置。这里提供了几种摆放的模式,Advanced Compact是参考原始位置进行摆放,Timing driven是参考cell的优先等级摆放,Exact Initial是按电路中位置就近放置,不调整位置。

如下模拟摆放的效果:

,时长00:51

NewCell可以看成初始位置后期可以对等到电路中的各器件位置,或对等与CustomCompiler中的place like schematic 后的初始布局位置。MoveCloser对cell进行布局优化。当前版本还有一些小问题需要优化,布局紧张时的cell 重叠问题和超出边界的问题

NewCell可以看成初始位置后期可以对等到电路中的各器件位置,或对等与CustomCompiler中的place like schematic 后的初始布局位置。MoveCloser对cell进行布局优化。当前版本还有一些小问题需要优化,布局紧张时的cell 重叠问题和超出边界的问题

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网