日志

Foundry不说的秘密:优化ESD设计提升芯片净利润?

| ||

当设计团队在为几十微瓦的功耗削减而欢呼时,一个占据着芯片边缘版图、直接影响着成本和可靠性的模块,却常常被当作“标准动作”而忽视——它便是ESD(静电放电)保护电路。我们习惯于选择Foundry提供的通用标准方案,但ESD设计,远非一项单纯的可靠性成本,而是贯穿于芯片成本结构、影响最终利润的关键杠杆。

ESD设计优化一般可直接减少芯片面积5%至40%,甚至超过50%,提升产品毛利。生产中单颗芯片的成本与芯片面积呈正相关。Foundry提供的通用标准ESD解决方案,例如基于GGNMOS(栅极接地NMOS)和RC触发Clamp的方案,以其稳健性和高工艺兼容性著称。但Foundry不会主动告诉你的是,这种稳健性往往以大面积为代价。通过采用更先进的ESD电路架构,如主动式TVS(瞬态电压抑制)钳位、动态反馈Clamp或经过精心优化的分布式设计,可以在满足同等ESD等级(如2kV HBM)的前提下,将单个IO的ESD保护面积显著减少,单位芯片的制造成本也随之下降。

图1 晶圆及芯片

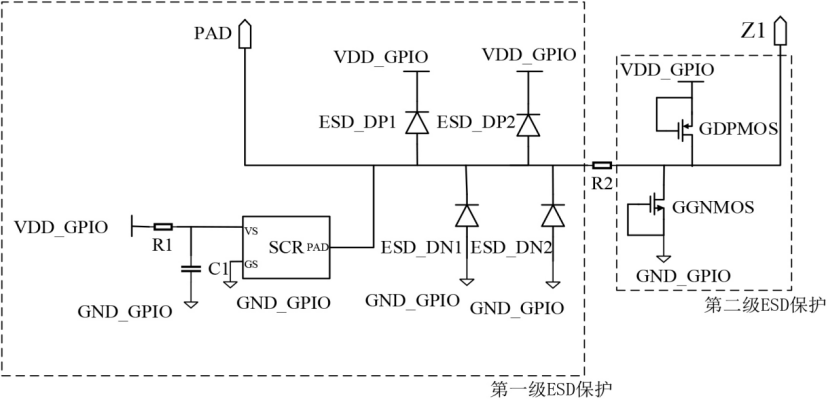

通过针对各接口性能优化ESD尺寸及结构,来增强产品的市场竞争力。Foundry的规则确保了ESD鲁棒性,但并未对不同IO的性能需求进行区分。一个用于烧录配置的低速GPIO与一个传输10Gbps信号的高速SerDes链路,若采用同样尺寸和结构的ESD保护,无疑是对高速链路性能的浪费与牺牲。通过对IO端口进行差异化ESD设计,为低速IO配置面积更小、成本更低的方案,为高速IO精心优化寻求保护强度与寄生效应之间的最佳平衡,这本身就是一种精准的成本控制。其次,更优的ESD设计意味着在同等工艺下能实现更高的接口性能,这为产品赢得了宝贵的市场差异化和定价权。

图2引脚接口电路保护结构示意图

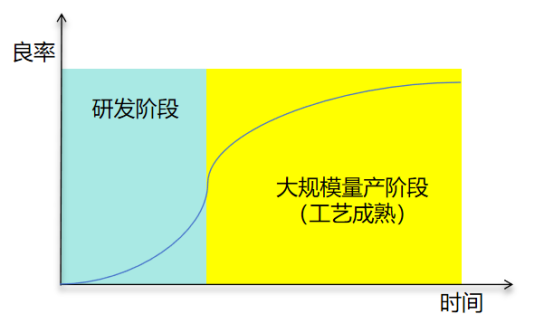

优化CDM保护,提升良品率。器件氧化层的持续薄化,使得芯片对CDM静电放电事件愈发敏感;而该问题固有的滞后性(通常在封装后暴露)则导致修复成本极高,且Foundry的设计手册对CDM防护的指导往往弱于HBM。然而,一个高效的CDM保护网络,其核心在于建立从Pad到电源轨之间具备低阻抗与全路径特性的电荷泄放通道。这远非单个IO单元内部优化所能及,它要求设计者对整个芯片的电源网络规划、Power Clamp的布局与响应速度、以及IO Ring的整体协同设计具有深刻的理解。优化CDM保护,直接关联着测试良率。在量产中,测试良率每增长一个百分点,其价值便以数百万美元计。通过降低CDM导致的测试失效,直接增加了可售芯片的数量,减少了废片损失。这不仅是成本的节约,更是对产能和交付承诺的有力保障。

图3 良率随时间发展的变化

在芯片设计竞争白热化的今天,当PPA的优化逐渐触及天花板时,对ESD这片“隐秘角落”的精耕细作,正成为决定产品商业成败的新前沿。ESD面积优化带来的晶圆成本节约、性能竞争力增强、测试良率提升带来的报废减少相加,这些所揭示的,正是那些被Foundry手册所隐藏,却可以通过精明的ESD设计,直接落入企业净利润中的宝贵财富。

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网