日志

GGNMOS(Gate-Grounded NMOS)的个人理解

热度 2| |

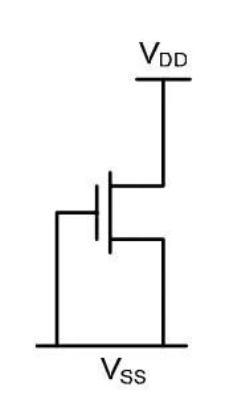

GGNMOS的工作原理:

正常状态:栅极接地(VSS),GGNMOS处于关闭状态,对核心电路无影响。

ESD事件期间:

雪崩击穿,高压ESD脉冲使NMOS的漏衬(darin-substrate)结发生雪崩击穿;

寄生NPN开启,雪崩击穿产生的空穴电流流向沉底(substrate),电流在衬底电阻上形成电压降Vbe;

寄生NPN导通,当Vbe超过0.7V时,寄生三极管NPN(darin-sub-source)导通;

泄放电流,寄生NPN进入snapback(回滞),提供一个电源地的低阻抗路径,ESD通过该路径泄放。

优点:设计简单、开启速度快(Vt1<反偏二极管),常用于IO引脚及电源地钳位

缺点:存在non-uniform snapback turn on,只要其中某根NMOS finger 到达Vt1(触发电压)进入snapback,由于Vh(snapback保持电压)<Vt1,其他NMOS finger就无法进入snapback,大电流累计在开通路径finger,当电流持续累积并且电压到达Vt2(二次击穿电压),NMOS局部热失效。

![]()

优化改善措施:

设计层面,在栅极与地之间加入一个电阻Rg(一般10kohm~100kohm),通过统一的电阻控制所有finger的导通,原理及好处如下:

栅极浮空:当加入电阻后,当ESD(ns级别)到来,栅极可以被视为"浮空”;

栅电容耦合:当ESD施加至漏极,通过NMOS的栅漏寄生电容(Cgd)的瞬态耦合电流注入到栅极节点;

栅电压抬升:耦合电流经过栅极统一的电阻Rg,在所有finger都产生压降Vg;

诱发表面导通:Vg会使得NMOS的所有finger表面沟道形成反型层,电流会通过沟道从漏极流到源极,产生空穴对流向衬底使得Isub上升,并且降低了寄生NPN的有效基区宽度,提升了电流增益β,对开启电流Isub要求降低;

雪崩击穿:尽管沟道在泄放电流,但ESD电流源太“强大”了,漏极电压仍然会继续上升,直至雪崩击穿漏衬二极管;

寄生NPN导通:当Vbe>0.7V,NPN均匀导通,远优于表面的MOS沟道通流能力。 电流会自动寻找阻抗最低的路径。因此,绝大部分的ESD大电流会迅速从“MOS沟道路径”切换到“寄生BJT路径”。

该方法可以使得导通更均匀,Vt1更小,开启更迅速,类似于GCNMOS结构原理。

注:若Rg太小,就接近于连接VSS,无效,若Rg太大,可能Vg>Vth,NMOS完全开启,ESD主要通过沟道泄放,烧毁器件。

器件层面,增大漏极width,增大漏极的接触孔到栅距离,中间铺上SAB(salicide block),好处如下:

增加了漏极镇流电阻,使得Vt2>Vt1,从而使得器件导通更均匀;

加强漏极的散热性能,漏极过高压大电流,热集中,salicide熔点低,易提前熔化降低ESD性能;

解决LDD带来的问题,避免电流聚集在漏极靠近栅极区域,使电流沿着漏衬PN结方向而不是沟道方向走。

以上仅为个人理解总结,若有误请指正,谢谢。

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网