日志

CoreLink CCI产品介绍(转)

| ||

1. CCI-550简介

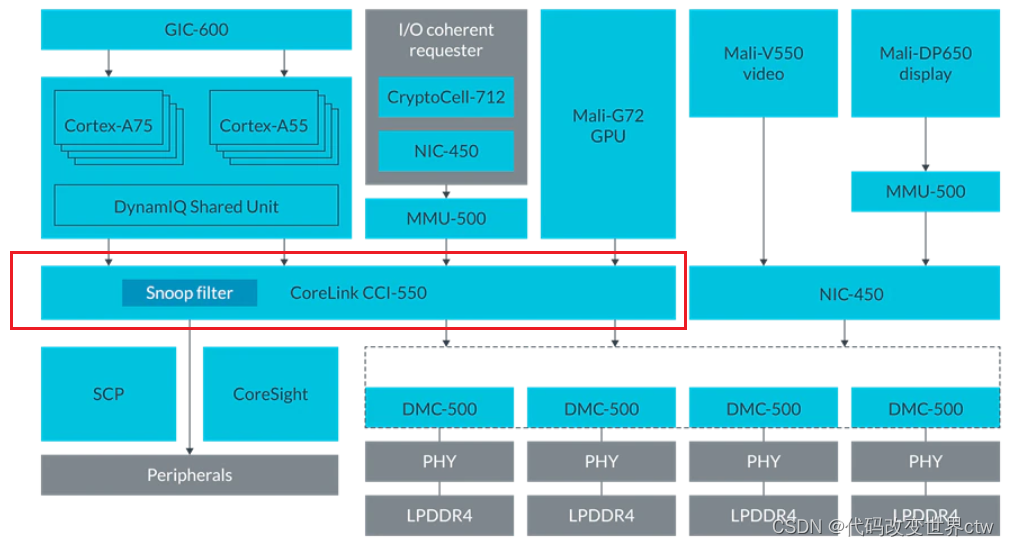

Arm CoreLink CCI-550 Cache Coherent Interconnect 扩展了CoreLink CCI-500。它在 big.LITTLE 处理器集群之间提供完整的缓存一致性,并为其他代理(如 Mali GPU、网络接口或加速器)提供 I/O 一致性。CoreLink CCI-550 提供可扩展和可配置的互连,使 SoC 设计人员能够以尽可能小的面积和功耗满足性能目标,并且还增加了可降低整体系统延迟的监听滤波器。

这里在总结以下,CCI-550到底是干嘛的? 是处理多Master之间的cache一致性的

那么CCI-550是怎样工作的呢?

CCI-550 允许ACE master和 ACE-Lite master组合,最多总共七个Master。

CCI-550 AXI4 master接口提供了与存储器和外设地址空间的连接接口。

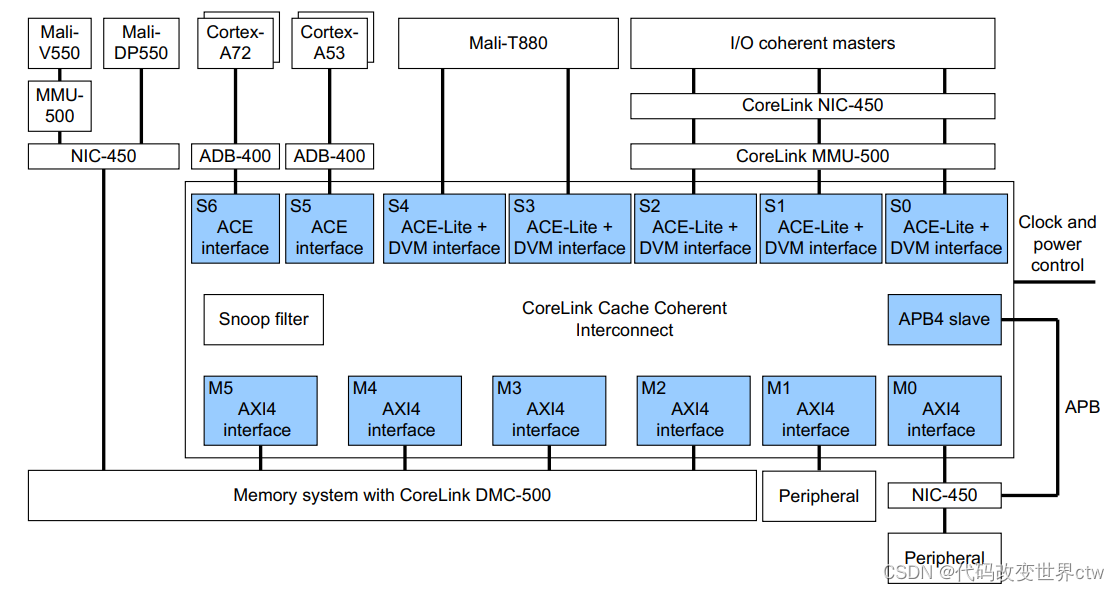

CCI-550 的特性结合起来提供可编程的高带宽互连hardware coherent系统。CCI-550 提供:

ACE masters之间的数据一致性。

Quality of Service (QoS) features for traffic management

输入和输出(I/O) 与 ACE-Lite master的一致性。

master和slaver之间的交叉开关互连功能。

一个性能监控单元(PMU),用于对与性能相关的事件进行计数。

用于MMU 之间通信的主设备之间的DVM 消息传输。

程序员视图(PV) 来控制一致性和互连功能。

侦听过滤器,可降低侦听功率并提高侦听未命中的性能。

支持 Arm TrustZone 技术以提供安全、非安全和受保护状态。

Snoop filter的介绍

CCI-550 包含一个包容性监听过滤器(snoop filter),用于记录存储在ACE 主缓存。

侦听过滤器可以在未命中的情况下响应侦听事务,并侦听适当的主控只有在命中的情况下。Snoop 过滤器条目通过观察来自 ACE 主节点的事务来维护以确定何时必须分配和取消分配条目。

侦听过滤器可以响应多个一致性请求,而无需向所有人广播ACE 接口。例如,如果地址不在任何缓存中,则监听过滤器会以未命中和将请求定向到内存。如果地址在处理器缓存中,则请求被视为命中,并且指向在其缓存中包含该地址的 ACE 端口。

Arm 建议您将 snoop 过滤器目录配置为总大小的 0.75-1 倍连接到 CCI-550 的处理器的独占缓存。监听过滤器是 8 路组关联的并且,为了尽量减少冲突,存储两倍于配置大小的标签。冲突的一个例子是当 CCI-550 无法在监听过滤器的可用位置插入新条目时。如果发生冲突发生,现有条目被逐出,并且监听过滤器向处理器发出 CleanInvalid 监听可能持有驱逐线。这种类型的驱逐被称为返回无效,并且预计如果您按照 Arm 建议配置监听过滤器大小,则很少发生。

监听过滤器是通过监控来自附加主节点的事务来更新的,这些主节点分配和将数据释放到它们的缓存中。在 ACE 协议中,干净数据的释放使用表示驱逐交易。

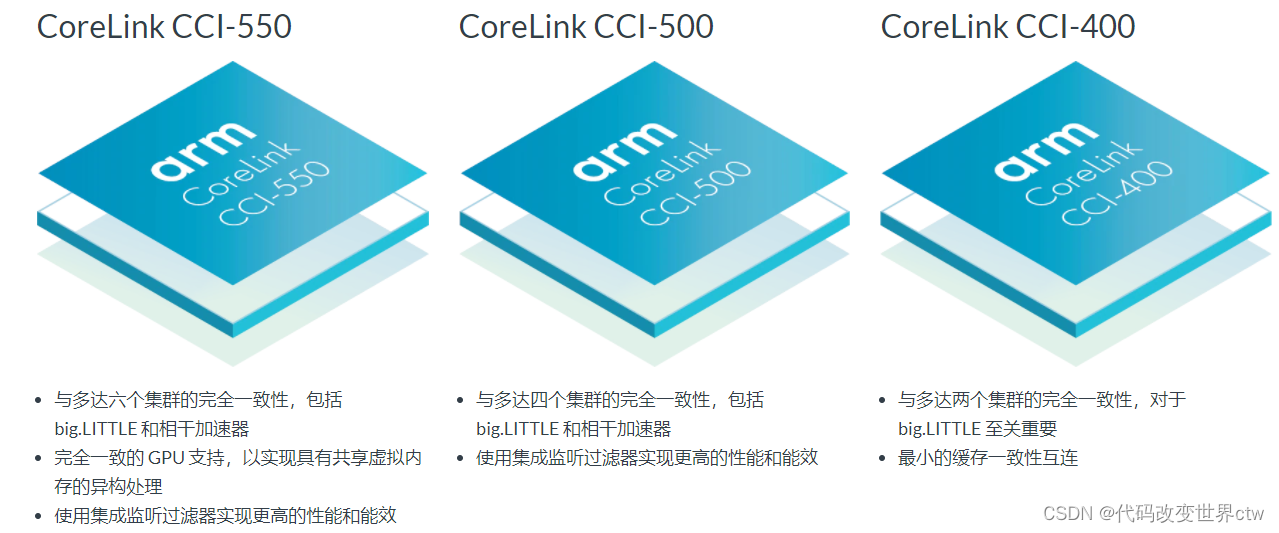

2. CoreLink Cache Coherent Interconnect Family 介绍

3. CI-700的介绍

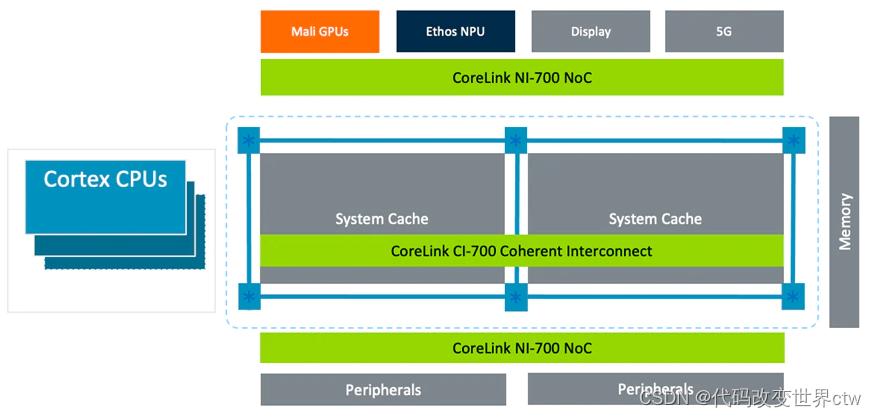

CoreLink CI-700 是一种可配置且可扩展的相干互连,采用 Armv9 处理器设计,可提供全面计算解决方案。作为专注于最新高端移动用例的解决方案的一部分,与其他 Arm IP 一起设计、验证并优化了性能和功率。它可以从主流智能手机扩展到高端智能手机,再到笔记本电脑级设备。设计与 CoreLink 网络互连和 CoreLink MMU-700 内存管理单元配对使用。

以全面计算解决方案为重点的方法使 CoreLink 系统 IP 能够与 Cortex-X CPU、Cortex-A CPU 和 Ethos NPU 无缝协作

ARM 提供了所有重要组件来移动和存储处理器和内存之间的数据。此类组件包括最近发布的 CCI-400 高速缓存一致性互连、NIC-400 网络互连、DMC-400 动态内存控制器和 MMU-400 系统内存管理单元以及极具特色的高速缓存控制器、DMA 控制器、静态内存控制器以及符合最高规格的内存接口 PHY。使用 AMBA 设计工具,可对 ARM 子系统进行轻松配置和验证并检测其性能。

参考

The Arm CoreLink CCI-550 Cache Coherent Interconnect

————————————————

原文链接:https://blog.csdn.net/weixin_42135087/article/details/121949852

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网