日志

Xilinx高性能NVMe Host控制器IP+PCIe 3.0软核控制器IP,4通道DMA,1通道IO,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3 ...

| |||

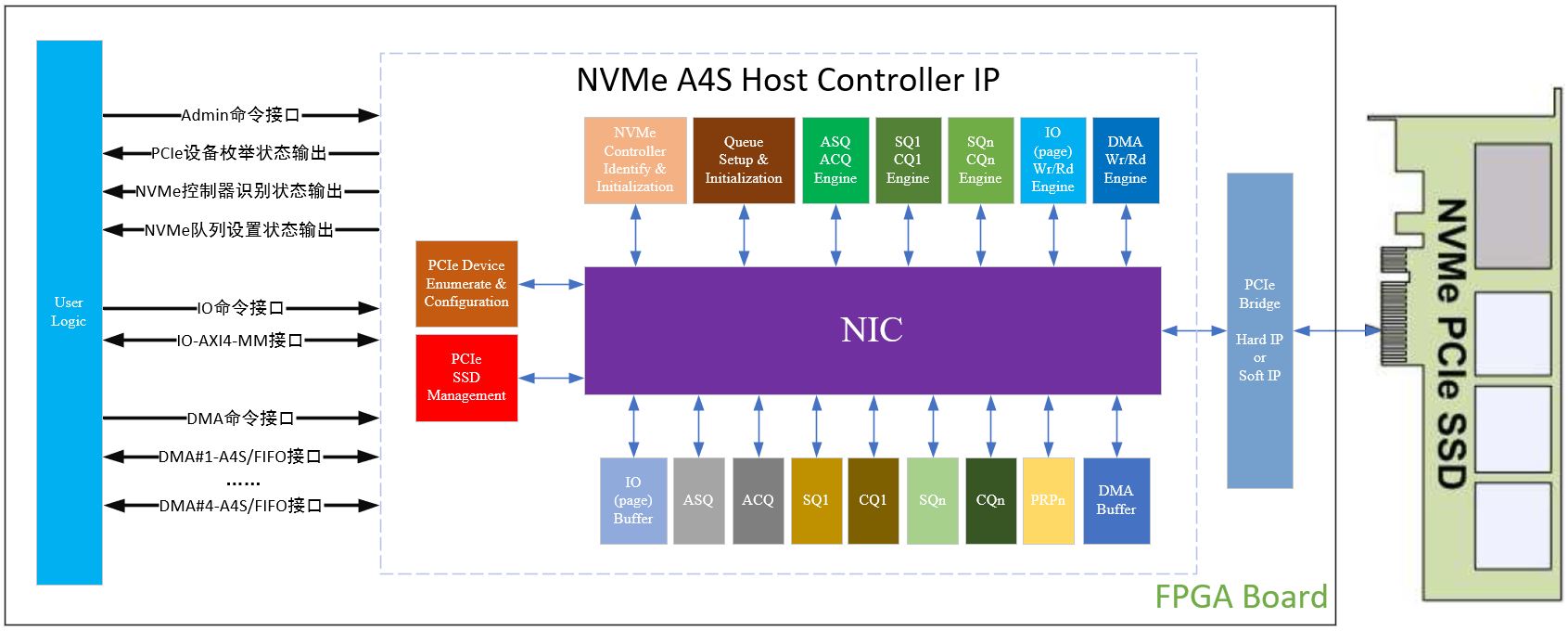

NVMe A4S Host Controller IP

1 介绍

NVMe A4S Host Controller IP可以连接高速存储PCIe SSD,无需cpu和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/fifo接口和数据读取AXI4-Stream/FIFO接口,适合于高性能、顺序访问的应用,比如视频记录、信号记录。

NVMe是基于PCIe之上的协议,NVMe A4S Host Controller IP通过PCIe Bridge连接并访问PCIe SSD。PCIe Bridge实现支持PCIe Hard IP或PCIe Soft IP。

无需CPU,NVMe A4S Host Controller IP自动执行对PCIe SSD的PCIe设备枚举和配置、NVMe控制器识别和初始化、NVMe队列设置和初始化,实现必须以及可选的NVMe Admin Command Set和NVM Command Set,实现对PCIe SSD的复位/断电/SMART/Error Information/Device Self-test管理、IO(Page)读写、DMA读写和数据擦除功能,提供用户一个简单高效的接口实现高性能存储解决方案。

NVMe A4S Host Controller IP DMA读写的顺序传输长度是在生成RTL时配置的,最小是4K-Byte,最大是512K-Byte。顺序传输长度配置为4K-Byte,NVMe Host Controller IP所消耗的BRAM最少,但是可以达到CrystalDiskMark测试软件RND4K Q32T16测试模式下的读写性能。顺序传输长度配置为128K-Byte,NVMe Host Controller IP所消耗的BRAM比较多,可以达到CrystalDiskMark测试软件SEQ128K Q32T1测试模式下的读写性能。

针对多路数据通道访问PCIe SSD,使用NVMe的多队列特性,NVMe Host Controller IP支持灵活配置DMA读写的通道个数,按照NVMe队列优先级仲裁(循环仲裁或加权循环仲裁)机制,实现多个DMA通道对同一块PCIe SSD的高效访问,从而达到多路数据通道访问的并行需求和QoS要求。

1.1 特性

Ø 支持Ultrascale+,Ultrascale,7 Series FPGA

Ø 支持PCIe Gen4,PCIe Gen3,PCIe Gen2 SSD

Ø PCIe Bridge实现支持PCIe Hard IP或PCIe Soft IP

Ø 无需CPU和外部存储器

Ø 自动实现对PCIe SSD的PCIe设备枚举、NVMe控制器识别和NVMe队列设置

Ø 支持对PCIe SSD的NVM Subsystem Reset、Controller Reset和Shutdown

Ø 支持NVMe Admin Command Set:Identify、SMART、Error Information、Device Self-test、Create/Delete IO Submission/Completion Queue、Set Features – Volatile Write Cache/Arbitration

Ø 支持NVMe NVM Command Set:Write、Read、Flush、Dataset Management

Ø 提供1个Admin命令接口,实现对PCIe SSD的复位/断电/SMART/Error Information/Device Self-test管理功能

Ø 提供1个IO命令接口,实现对PCIe SSD的IO(Page)读写、Cache Flush和逻辑数据块擦除功能;提供1个IO-AXI4-MM接口读写IO(page)数据

Ø 提供1个DMA命令接口,实现对PCIe SSD的DMA读写功能

n 提供1个DMA-AXI4-Stream-In/Out或DMA-FIFO-In/Out接口实现DMA数据的输入和输出

Ø 支持SGDMA

Ø DMA读写的顺序传输长度可以配置,4K-Byte~512K-Byte;不同的顺序传输长度对应不同的DMA读写性能,同时也消耗不一样的BRAM资源

Ø 针对多通道DMA需求,可以配置4个DMA命令接口,4个DMA-AXI4-Stream-In/Out或DMA-FIFO-In/Out接口

Ø NVMe队列的个数(配置DMA通道的个数)和深度可配置,平衡对PCIe SSD的DMA性能和消耗的逻辑资源

Ø 支持循环仲裁(Round Robin Arbitration)和加权循环仲裁(Weighted Round Robin Arbitration)

Ø 支持NVMe Admin和IO命令的超时和错误处理恢复机制,提供详尽以及扩展的访问错误状态输出

Ø 支持的NVMe设备:

n Base Class Code:01h(mass storage),Sub Class Code:08h(Non-volatile),Programming Interface:02h(NVMHCI)

n MPSMIN(Memory Page Size Minimum):0(4K-byte)

n LBA Unit:512-byte,1024-byte,2048-byte或4096-byte

Ø 一个NVMe A4S Host Controller IP直接连接到PCIe SSD

Ø 易于集成的同步、可综合verilog设计

Ø 通过完全验证的NVMe A4S Host Controller IP

2 概述

NVMe A4S Host Controller IP作为一个对PCIe SSD的高性能存储控制器,不但提供对PCIe SSD的配置管理功能,而且提供对PCIe SSD的IO(Page)读写以及DMA读写功能。

NVMe A4S Host Controller IP具备PCIe SSD Management,实现对PCIe SSD的复位/断电/SMART/Error Information/Device Self-test管理功能。

NVMe A4S Host Controller IP具备ASQ/ACQ引擎,实现NVMe Admin Command Set:Identify、SMART、Error Information、Device Self-test、Create/Delete IO Submission/Completion Queue、Set Features – Volatile Write Cache/Arbitration。

NVMe A4S Host Controller IP具备IO(Page) Wr/Rd引擎和SQ1/CQ1引擎,实现对PCIe SSD的IO(Page)读写、Cache Flush和逻辑数据块擦除功能。

NVMe A4S Host Controller IP具备DMA Wr/Rd引擎和SQn/CQn引擎,实现对PCIe SSD的DMA读写功能。

上电后,NVMe A4S Host Controller IP内置的PCIe Device Enumerate & Configuration自动实现对PCIe SSD的PCIe设备枚举和配置;然后内置的NVMe Controller Identify & Initialization自动实现对PCIe SSD的NVMe控制器识别和初始化;最后内置的Queue Setup & Initialization自动实现对PCIe SSD的NVMe队列设置和初始化。至此,NVMe A4S Host Controller IP完成对PCIe SSD的所有配置和初始化工作,可以开始提供对PCIe SSD的读写、擦除、复位、断电、SMART、Device Self-test操作。

图 2 NVMe A4S Host Controller IP结构框图

3 产品规格

3.1 性能

PCIe配置参数:Max Payload Size=256-byte,Max Read Request Size=512-byte

1. PCIe Gen3 SSD(三星990 Pro 4TB),Seq=128KB,1个DMA通道:

a) DMA写入速度3380MB/s

b) DMA读取速度3550MB/s

2. PCIe Gen3 SSD(三星970EVO Plus 1TB),Seq=128KB,1个DMA通道:

a) DMA写入速度3050MB/s

b) DMA读取速度3350MB/s

3. PCIe Gen3 SSD(Intel D5-P5530 3.84TB),Seq=128KB,1个DMA通道:

a) DMA写入速度3280MB/s

b) DMA读取速度2700MB/s

4. PCIe Gen3 SSD(DapuStor R5101 3.84TB),Seq=128KB,1个DMA通道:

a) DMA写入速度3380MB/s

b) DMA读取速度3510MB/s

5. PCIe Gen3 SSD(三星970EVO Plus 1TB),Seq=4KB,1个DMA通道:

a) DMA写入速度2700MB/s

b) DMA读取速度2000MB/s

3.2 资源

1. KU040

表3.1 PCIe Gen3 SSD,Seq=128K,Queue Depth=4,1-DMA

LUTs | FFs | BRAMs | PCIe | |

总资源 | 16896 | 23763 | 87 | 1 |

NVMe Host Controller | 11437 | 15813 | 70 | 0 |

PCIe Bridge(Hard IP) | 5462 | 7950 | 17 | 1 |

LUTs | FFs | BRAMs | GT | |

总资源 | 66920 | 60221 | 86 | 4 |

NVMe Host Controller | 11437 | 15813 | 70 | 0 |

PCIe Bridge(Soft IP) | 55055 | 43411 | 16 | 0 |

PCIe PHY | 291 | 724 | 0 | 4 |

表3.2 PCIe Gen3 SSD,Seq=128K,Queue Depth=4,2-DMA

LUTs | FFs | BRAMs | PCIe | |

总资源 | 22308 | 30798 | 155 | 1 |

NVMe Host Controller | 16838 | 22831 | 138 | 0 |

PCIe Bridge(Hard IP) | 5470 | 7958 | 17 | 1 |

表3.3 PCIe Gen3 SSD,Seq=128K,Queue Depth=4,4-DMA

LUTs | FFs | BRAMs | PCIe | |

总资源 | 41308 | 44798 | 283 | 1 |

NVMe Host Controller | 36297 | 36884 | 266 | 0 |

PCIe Bridge(Hard IP) | 5470 | 7958 | 17 | 1 |

表3.4 PCIe Gen3 SSD,Seq=4K,Queue Depth=8,1-DMA

LUTs | FFs | BRAMs | PCIe | |

总资源 | 16184 | 22046 | 31 | 1 |

NVMe Host Controller | 10719 | 14096 | 14 | 0 |

PCIe Bridge(Hard IP) | 5470 | 7948 | 17 | 1 |

表3.5 PCIe Gen3 SSD,Seq=4K,Queue Depth=8,2-DMA

LUTs | FFs | BRAMs | PCIe | |

总资源 | 20908 | 27361 | 43 | 1 |

NVMe Host Controller | 15438 | 19402 | 26 | 0 |

PCIe Bridge(Hard IP) | 5470 | 7959 | 17 | 1 |

表3.6 PCIe Gen3 SSD,Seq=4K,Queue Depth=8,4-DMA

LUTs | FFs | BRAMs | PCIe | |

总资源 | 38686 | 38812 | 67 | 1 |

NVMe Host Controller | 33188 | 30833 | 50 | 0 |

PCIe Bridge(Hard IP) | 5503 | 7979 | 17 | 1 |

2. ZU7EV

表3.7 PCIe Gen3 SSD,Seq=128K,Queue Depth=4,1-DMA

LUTs | FFs | BRAMs | URAM | PCIe | |

总资源 | 22621 | 32978 | 40 | 8 | 1 |

NVMe Host Controller | 11311 | 15896 | 6 | 8 | 0 |

PCIe Bridge(Hard IP) | 11310 | 17082 | 34 | 0 | 1 |

表3.8 PCIe Gen3 SSD,Seq=128K,Queue Depth=4,2-DMA

LUTs | FFs | BRAMs | URAM | PCIe | |

总资源 | 27889 | 40021 | 44 | 16 | 1 |

NVMe Host Controller | 16592 | 22932 | 10 | 16 | 0 |

PCIe Bridge(Hard IP) | 11310 | 17089 | 34 | 0 | 1 |

表3.9 PCIe Gen3 SSD,Seq=128K,Queue Depth=4,4-DMA

LUTs | FFs | BRAMs | URAM | PCIe | |

总资源 | 47610 | 53994 | 52 | 32 | 1 |

NVMe Host Controller | 36297 | 36884 | 18 | 32 | 0 |

PCIe Bridge(Hard IP) | 11314 | 17110 | 34 | 0 | 1 |

表3.10 PCIe Gen3 SSD,Seq=4K,Queue Depth=16,1-DMA

LUTs | FFs | BRAMs | URAM | PCIe | |

总资源 | 22656 | 32339 | 40 | 2 | 1 |

NVMe Host Controller | 11358 | 15259 | 6 | 2 | 0 |

PCIe Bridge(Hard IP) | 11298 | 17080 | 34 | 0 | 1 |

表3.11 PCIe Gen3 SSD,Seq=4K,Queue Depth=16,2-DMA

LUTs | FFs | BRAMs | URAM | PCIe | |

总资源 | 28016 | 38747 | 44 | 4 | 1 |

NVMe Host Controller | 16714 | 21661 | 10 | 4 | 0 |

PCIe Bridge(Hard IP) | 11306 | 17086 | 34 | 0 | 1 |

表3.12 PCIe Gen3 SSD,Seq=4K,Queue Depth=16,4-DMA

LUTs | FFs | BRAMs | URAM | PCIe | |

总资源 | 47138 | 51456 | 52 | 8 | 1 |

NVMe Host Controller | 35828 | 34345 | 18 | 4 | 0 |

PCIe Bridge(Hard IP) | 11319 | 17111 | 34 | 0 | 1 |

4 交付清单

可交付资料:

1. 详细的用户手册

2. 设计文件:源代码或网表

3. 时序约束

4. 测试或Demo工程

5. 技术支持:邮件,电话,现场,培训服务

全部作者的其他最新日志

- • 基于PCIe(XDMA)的多路(1-32路)信号采集与回放子系统, 多路视频、AD、光纤等信号,支持PR over PCIe

- • 高性能PCIe 3.0软核,x1~x16,支持EP/RC,AXI4接口,内置DMA控制器,适用ASIC和FPGA

- • 基于LZO的无损数据压缩IP,高性能32Gbps,适用于FPGA&ASIC

- • Xilinx高性能低延时8通道PCIe-DMA控制器IP,SGDMA,QDMA,CDMA,RDMA, V4L2驱动,高速视频采集, 高速AD采集

- • Xilinx高性能NVMe Host控制器IP,4通道DMA,1通道IO,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和PCIe 4.0

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网