日志

芯片设计师的护身符:ESD防护设计的“三大法宝”

| ||

半导体芯片设计中处处藏着陷阱,设计师们需时刻防备,其中静电放电(ESD)就是一个巨大的潜在威胁。静电放电呈现的瞬态高电压、大电流冲击,往往几纳秒,就对芯片造成不可逆的破坏。为了抵御这种威胁,芯片设计师们掌握了三大核心防护技术——二极管、电阻与电源钳位,我们也称它们是ESD防护的“三大法宝”。

第一法宝:二极管——电荷的“定向疏导者”

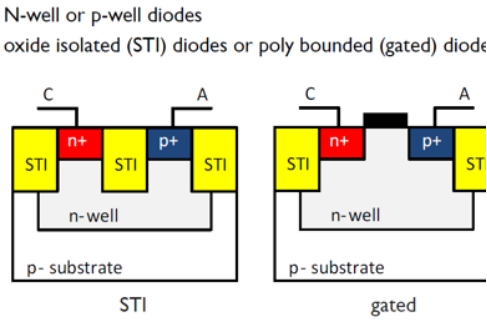

二极管是静电放电保护电路的基础组成部分之一,其功能主要依托于PN结的单向导通特性实现。

在电路常规工作电压下,用于静电放电防护的二极管处于反向截止状态,它的漏电流极小,基本不会对电路的正常运行有影响。若电压超过二极管的击穿电压(对于正向ESD脉冲)或反向击穿电压(对于负向ESD脉冲),这时二极管能迅速导通,形成一条低阻抗路径来释放电流从而保护电路。

图1 二极管

当代芯片采用的二极管静电防护结构,响应速度已能达到纳秒级,能够在大规模集成电路受损之前,迅速将静电能量引导分流。

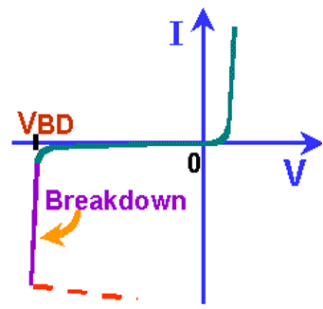

第二法宝:电阻——能量的“缓冲调节器”

如果说二极管是快速反应的“突击队”,那么电阻就是沉稳的“防御工事”。在ESD防护电路中,电阻主要起着限制电流与分配电压的关键作用。

日常设计中,我们往往会在输入/输出端口串联电阻,这样可以有效抑制ESD过程中产生的瞬态峰值电流过大。依据欧姆定律,当静电放电高压作用于电路时,电阻将分担部分电压,以达到降低传递到内部核心电路所承受的过压风险。同时,电阻与后级寄生电容形成RC网络,延长ESD脉冲的上升时间,降低其频率成分,使后续保护电路有更充分的时间响应。

图2 电阻

小编提醒,电阻在承受静电放电冲击时也可能发生损坏,设计电路时必须保证其具有足够的功率耐受性。先进的工艺中,还会采用分布式电阻结构,这使得静电放电能量可以更加均分到整个电阻网络中。

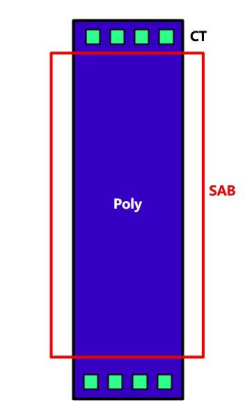

第三法宝:电源钳位——系统的“电压稳定器”

电源钳位是芯片级ESD防护系统的“最后防线”,负责维护电源轨之间的电压稳定,防止因电源反弹(latch-up)导致的系统失效。

电源钳位电路起作用的关键点在于,芯片正常工作时它保持高阻抗和极低的静态电流消耗;而在ESD事件期间,当电源电压异常升高时,迅速转变为低阻抗状态,在电源轨与地之间搭建一条有效的放电通路。

图3 全芯片ESD网络

先进的电源钳位设计能够在1-2纳秒内响应,维持电源电压在安全范围内,其触发阈值通常设定为常规电源电压的1.2至1.5倍,此类设计能在不影响电路正常工作的前提下,及时提供防护。

“三大法宝”的协同作战

实际上,二极管、电阻与电源钳位电路这三种核心防护手段通常并非独立运作,而是共同构建起一个多层次、立体化的静电放电防护体系:

第一级防护:芯片引脚处的二极管网络,对静电放电事件作出快速响应。

第二级防护:串联电阻,限制电流并延缓脉冲上升时间

第三级防护:电源钳位电路,确保整个电源域的稳定性

这种分级防护策略遵循“先疏导,后限流,再稳压”的原则,逐级消耗ESD能量,以保障内部核心电路的安全。

静电放电防护设计是保障芯片可靠性的关键工艺环节,而二极管、电阻和电源钳位这“三大法宝”构成了防护体系的基石。对于专业的芯片设计工作者来说,熟练掌握这些基础元件的特性与应用方法,是必备技能,也是确保芯片在复杂应用场景下长期稳定运行的重要基础。在半导体技术不断前进的道路上,这“三大法宝”也将继续演进,为每一代芯片提供坚实的防护盾牌,守护着集成电路世界的精密与秩序。

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网