日志

Inspiring and encouraging work——ISSCC 2006远东杰出论文奖背后的故事 ... ... ... ...

热度 1| ||

本文转发于知乎:关耳小兽:在芯片上放置四百多个螺旋电感——获得ISSCC远东杰出论文奖是一种什么体验?

感兴趣的话可以关注微信公众号:关耳小兽观察室

Daring to Put 400 Spiral Inductors on a Chip:Deong Kyoon Jeong的灵感和鼓励使不可能成为可能——一篇来自Jaeha Kim教授的回忆短文,记录了其在Deong Kyoon Jeong组里设计40G发射机的故事。

https://doi.org/10.1109/MSSC.2023.3334231

在2003年,我加入了韩国首尔国立大学郑德坤(Deog-Kyoon Jeong)教授的研究小组,担任博士后研究员。我在斯坦福大学获得了博士学位,而在合格的大学实验室进行研究是免除韩国严格兵役义务的一种途径。

2003年秋季,我们小组庆祝了10Gb以太网收发器芯片的成功运行,并且该芯片被ISSCC接受。在一次会议上,郑教授说:“这个眼图非常干净漂亮。”他一边在10Gb/s的眼图开口中间画两个“X”,一边继续说:“也许我们可以在这里和那里增加更多的过渡。然后我们就可以做一个40Gb/s的链路。”有人立即回答道:“教授,那会变成30Gb/s,而不是40Gb/s。”郑教授点了点头,但不打算改变计划。他看着我说:“金博士,我希望你设计一个40Gb/s的链路,用于下一次130纳米流片。”

会议结束后,我的座位伙伴李奉俊走过来,显得有些担忧地说:“你不会接受那个任务的,对吧?那简直太疯狂了!”是的,那是疯狂的。事实上,我的斯坦福大学博士导师马克·霍洛维茨教授曾经教我一种估算有线收发器在给定工艺技术下的最大可达比特率的方法,我知道40Gb/s已经超出了极限。

在130纳米CMOS中,考虑~60ps延时、扇出为4(FO4)的反相器,以非归零(NRZ)信号传输的40Gb/s比特率意味着每个比特时间必须是0.42个FO4长(25ps),即使采用最短的时钟周期,约7倍FO4,也需要进行16:1的时分复用,即使采用保守的缩放,这个速度在当今的7纳米技术中相当于280Gb/s的NRZ!郑教授的目标显然过高了。

但我想到:“我为什么要在这里玩得那么保守呢?毕竟,是郑教授发起并支持了这个项目。即使失败,我也不会有所损失。此外,我周围有郑教授最优秀的学生可以帮助我设计这个芯片,而且他的公司,Silicon Image,也支持集成电路制造、定制封装甚至测量!如果放过了这个机会,我就太愚蠢了。”因此,作为第一步,我开始着手设计一个40Gb/s的发射机。

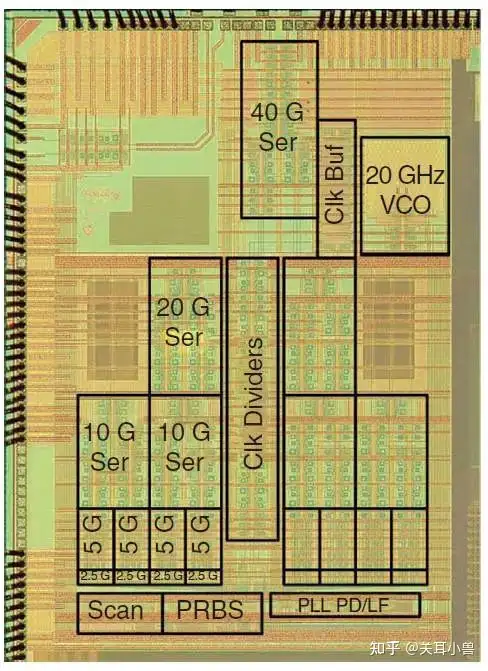

我首先将这个艰巨的任务分解成一系列较小的问题。很快我意识到,为了构建一个40Gb/s的发射机,我只需要使四个基本电路模块正常工作。这些在图2中用蓝色突出显示的电路模块包括:20GHz的振荡器,20 GHz的分频器,20 GHz的锁存器,40 Gbps的2:1多路复用器和40 Gbps的缓冲级。一旦我有了这五个部分,我就可以使用它们将32个并行数据流串行化为一个单一的40 Gbps数据流。结果设计可能会消耗大量功率,但这只是一个次要的考虑。我只需要让这个发射机工作!

发表在[3]中的40 Gbps发射机的体系结构。PRBS:伪随机比特序列;SER:串行器;MUX:多路复用器;BUF:缓冲区;PLL:锁相环;PFD:相频检测器;CP:电荷泵;LF:环路滤波器;VCO:压控振荡器;/2:除以2。

发表在[3]中的40 Gbps发射机的体系结构。PRBS:伪随机比特序列;SER:串行器;MUX:多路复用器;BUF:缓冲区;PLL:锁相环;PFD:相频检测器;CP:电荷泵;LF:环路滤波器;VCO:压控振荡器;/2:除以2。

我探索了到目前为止已知的所有最佳拓扑结构,包括静态CMOS门、动态CMOS门、电流模式逻辑(CML)门,甚至是Cherry–Hooper放大器。我能够得到的最佳带宽只有13 GHz,远低于40 GHz的目标带宽。前景看起来非常暗淡。然而,郑教授鼓励我进一步探索。然后我开始探索电感峰值的使用,这是我在斯坦福大学Thomas Lee教授的课堂上第一次学到的。我记得他在课堂上说,这是一种旧的增加带宽的技术,用于在1930年代构建带有缓慢真空管的高带宽视频放大器。他还补充说:“这就是为什么人们以前在接收信号不好的时候会敲电视机箱。敲击电视机箱有时会重新调整其中的电感线圈,使放大器再次工作!”这个想法似乎非常有前途。根据Lee的书籍,我可以使用多种电感峰值拓扑结构,例如并联峰值、串联峰值、并联串联峰值和桥式T线圈峰值。在其中,桥式T线圈峰值提供了2.8倍的带宽提高!令人鼓舞的是,一些研究论文,如[5],已经在克服类似带宽限制方面使用桥式T线圈峰值。

我继续并在CML缓冲级中添加了一个桥式T线圈负载。首先使用理想电感进行的交流分析结果起初看起来非常有希望,但包括芯片上螺旋电感的寄生参数在内的瞬态模拟结果并不理想。原因是多方面的。来自[4]的理论电感值在考虑到寄生参数时并不是最佳的。此外,晶体管的栅极和扩散电容是非线性的,其值取决于电压条件。这意味着为小信号交流响应优化的电感值可能不适用于大信号瞬态响应。例如,即使缓冲器的大小具有最大平坦的群延迟响应,其大信号阶跃响应仍然存在显著的过冲和振荡。

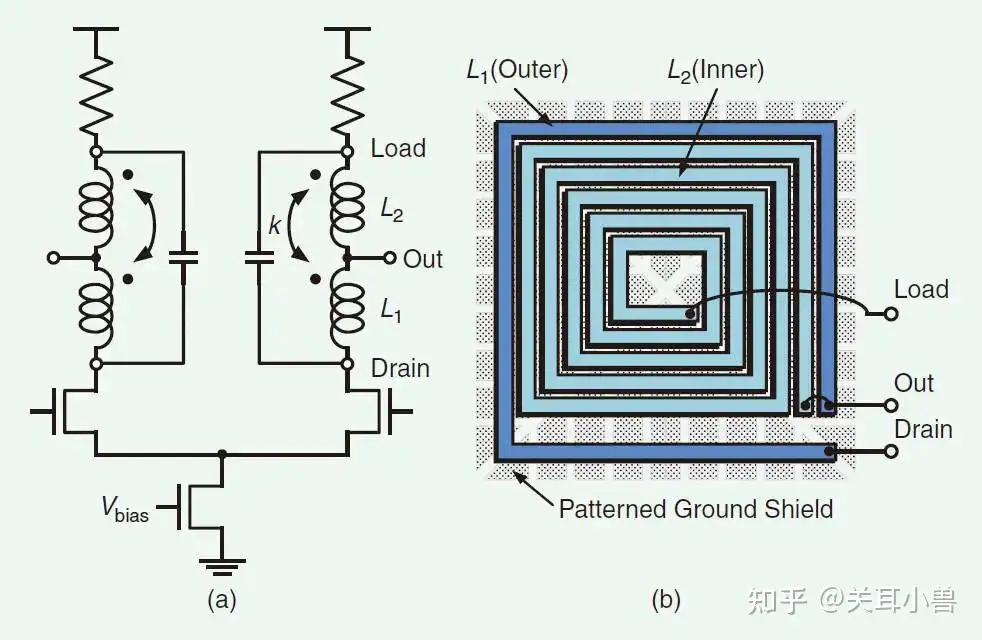

(a) 具有桥接T型线圈峰值的CML缓冲器和(b)具有负耦合系数(k<0)的螺旋T型线圈的布局。

(a) 具有桥接T型线圈峰值的CML缓冲器和(b)具有负耦合系数(k<0)的螺旋T型线圈的布局。

为了解决这个问题,我不得不求助于优化技术。我设计了一个混合优化算法,如[6]所述,它在ASITIC和HSPICE两个工具之间交替使用。通过ASITIC,我找到了最佳的芯片内螺旋T线圈布局,最小化了给定电感值的寄生电容。通过HSPICE,我调整了电感值以获得更好的瞬态响应,考虑到提取的T线圈和晶体管的寄生参数。然后,使用一些随机扰动重复此过程,以帮助全局收敛。整个优化过程由MATLAB和Perl脚本自动化,但仍需约5小时才能找到解决方案。

由于一些错误,最初的几次尝试产生了荒谬的结果。经过调试后,优化器输出了难以置信的结果:它说我可以构建一个带有41.9 GHz带宽、6.5 ps上升时间和无阶跃过冲的CML缓冲器。这几乎是带宽的三倍改进!这些电感器太神奇了。

但是当我仔细查看优化后的参数值时,有些不对劲。T线圈的两个耦合电感器之间的耦合系数(k)的符号是负号,而不是正号。糟糕。我忘了限制它的极性。我的原始计划是将T线圈的两个耦合电感器实现为一个单螺旋结构,并且耦合系数必须为正。我添加了约束并重新运行了优化。但结果不如以前好。经过几次尝试后,我决定只是翻转螺旋的内部部分,使耦合系数反转。这看起来很奇怪,但模型和仿真表明它将表现得更好!只有一个方法可以弄清楚它是否有效:去构建它。

在郑教授小组的研究生的强力帮助下,特别是金正谦和李奉俊,我能够找到了40Gbps 2:1多路复用器和20GHz锁存器的最佳设计,并将它们组合在一起构建了一个40Gbps的发射机。我们没有足够的时间重新优化用于较慢速度的构建块,最终在所有地方都使用了针对20GHz和40Gbps优化的构建块。由此产生的设计变得非常庞大,占据了近2.5 × 3.6平方毫米的面积,包含了410个螺旋T线圈。这仍然是我迄今为止构建的最疯狂的芯片。

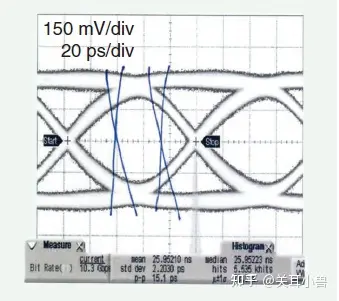

审判日在流片后的几个月后到来。测试一开始进行得很顺利。20GHz的锁相环锁定了,发射机通过球栅阵列封装以40Gbps产生了开放的眼图。万岁!但是,首尔国立大学示波器的带宽和时序精度不足以测量干净的40Gbps眼图。我不得不将测试板带到加州圣尼维尔的Silicon Image公司,使用更好的设备完成测量。

我在Silicon Image测量的第一个40Gbps眼图看起来确实更干净但是奇怪。您可以看到上升和下降的过渡有两个明显的轨迹。尽管如此,还有很多值得庆祝的事情。输出摆幅达到了预期的约500毫伏,时序抖动足够低,可以进行40Gbps操作。即使有分裂的轨迹,我们仍然有一个开放的40Gbps眼图,这是令人惊讶的。

然而,我无法停止思考是什么导致了分裂。即使在准备ISSCC提交时,我也不能声称我们有一个完全工作的发射机。在与郑教授讨论后,我们将论文标题从“A Fully Integrated 40 Gb/s Transmitter”更改为“Circuit Techniques for a 40-Gb/s Transmitter”。

即使论文被接受,我也无法享受它。ISSCC的人们会询问这个问题,而我没有答案。

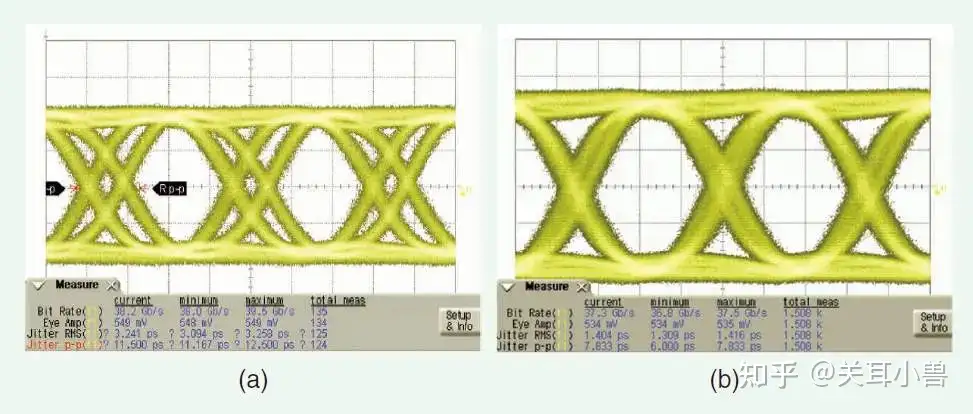

但很快我们发现,这与阶段之间的额外布线有关。该线路有效地为螺旋电感器增加了四分之一的匝数,增加了其电感。结合CML缓冲器的限制作用,它导致了数据相关的时序抖动,这在眼图中表现为分裂的轨迹。

在发现根本原因后不久,我们能够找到一个解决方法。增加的电感导致的影响可以通过增加负载电阻来补偿,我可以通过使用聚焦离子束修剪掉一些并联布置的电阻来实现。郑教授支持了另一次前往Silicon Image的行程,我能够获得更好看的眼图和更强的信心。我们对这个过程及其结果都感到非常满意。郑教授说:“伟大的工程师不是那些第一次就成功的人。他们是那些在失败后一次又一次地努力的人。”霍洛维茨教授评论说:“当人们得到愿景和支持时,他们能够实现令人惊讶的成就。”

郑教授的团队在ISSCC 2006上获得杉野拓夫远东杰出论文奖的照片,因为他们设计了0.13μm CMOS的40 Gbps发射机。

关于作者

金宰河(jaeha@snu.ac.kr)于1997年获得首尔国立大学学士学位,并于1999年和2003年分别从斯坦福大学获得硕士和博士学位。他是韩国首尔国立大学的教授,邮编08226。他的研究兴趣包括低功耗混合信号电路及其设计方法。他于2015年创立了Scientific analog, Inc.,开发了用于模拟/混合信号建模和Systemverilog模拟的电子设计自动化工具。他曾获得2005年国际固态电路会议(International Solid-State Circuits Conference)的菅野拓男杰出远东论文奖,并于2020年被韩国国家工程院评为韩国前100位技术领袖。

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网