日志

PCIe Base Address空间深度解析

| |||

此文章摘抄自微信公众号"芯塾科技",如有侵权,请联系删除,谢谢!

1.文章坚持实际工作中有所帮助---实际工作中遇到问题可查阅。

2.章节内容规划具有连贯性。lspci-setpci-PCIe Configuration Space--next。

3.文章以文字和视频形式发布,建议大家视频和文章结合查阅。

4.视频发布:公众号、B站、抖音,搜寻“芯塾科技”可观看。

5.文章发布: 公众号、CSDN、知乎、B站,搜寻“芯塾科技”可浏览。

2.引入PCIe Base Address原由

1.本文先不直接引入PCIe Base Address概念,先思考下如下问题。

2.AMD GPU为例。

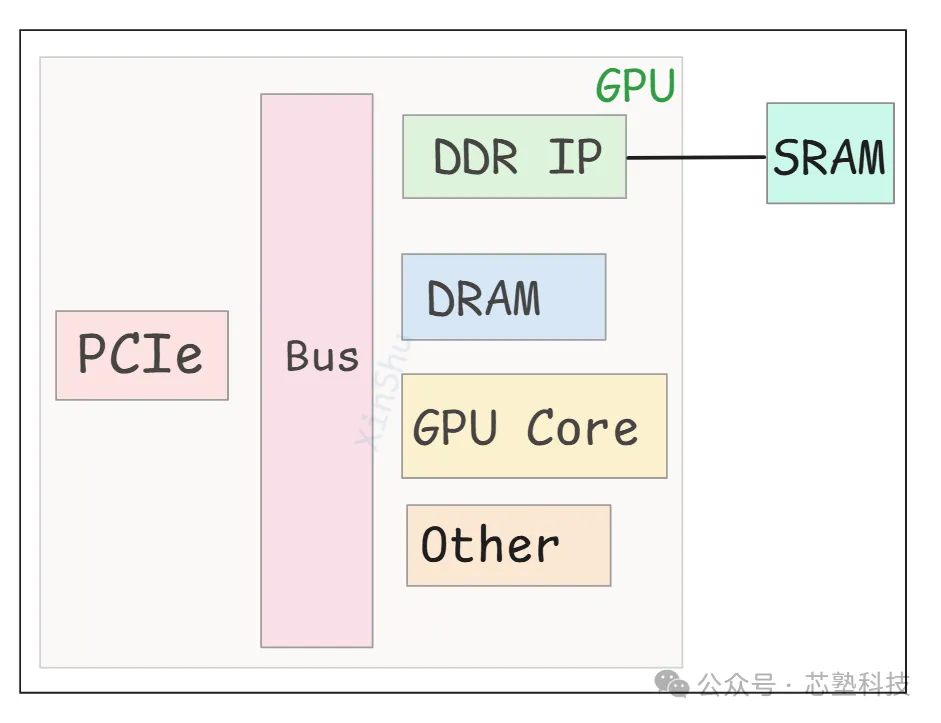

3.AMD GPU内部逻辑结构

3.AMD GPU内部逻辑结构

4.GPU内部SRAM/DDR,cpu如何访问呢?

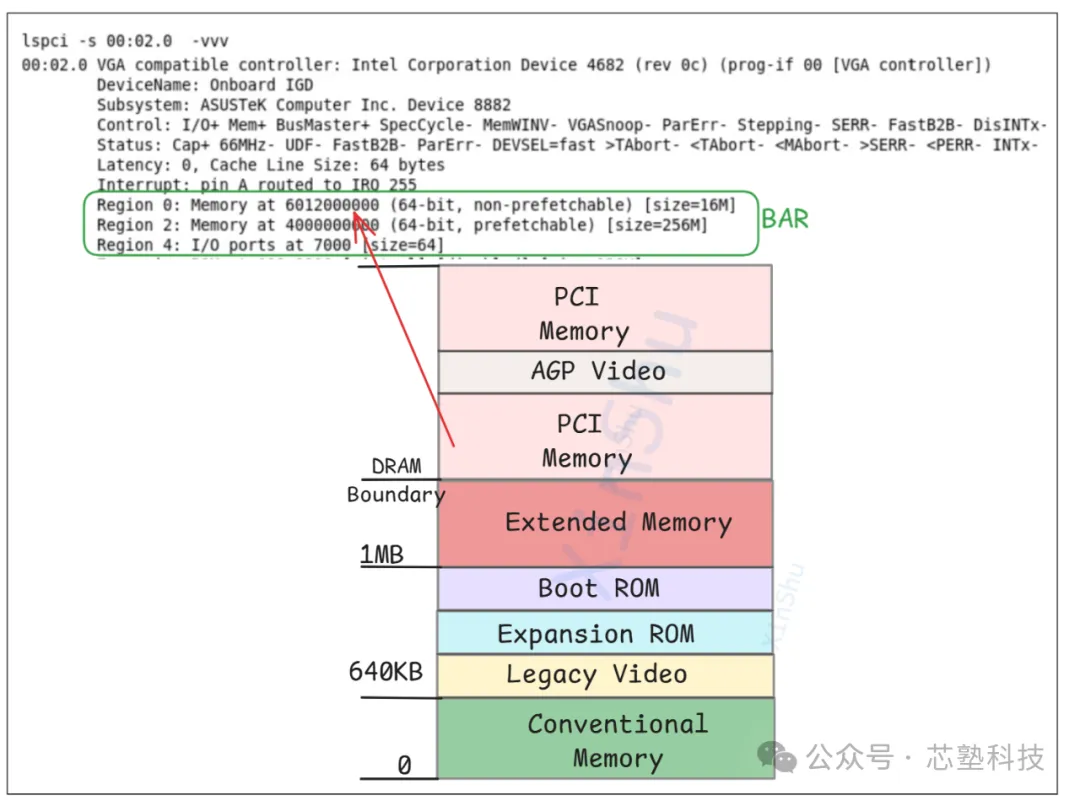

5.CPU访问外部设备存在内存映射(memory mapped)和 IO映射(I/O Mapped)两种方式。

6.CPU内部Mem空间、IO空间给GPU划分部分空间,CPU通过Mem/IO指令生成的mem/IO事物,访问GPU资源。

7.CPU发出的memory/IO请求,Root Complex转换为PCIe配置mem/IO事物报文。

7.CPU发出的memory/IO请求,Root Complex转换为PCIe配置mem/IO事物报文。

8.CPU 需要给PCIe设备分配的空间类型,是mem还是io空间?

9.CPU需要给PCIe设备分配的mem/io空间的大小?

10. 如上信息需要通过PCIe设备提供一种能力/寄存器即PCIe Bar Address

3.Introduction PCIe Base Address

1.PCI协议规定PCI配置头空间,实现6个寄存器,分别位BAR0~BAR5。

2.Base address寄存器格式

2.Base address寄存器格式

3.根据Bar type,PCIe Bar分为两种类型Mem BAR/IO BAR。

3.根据Bar type,PCIe Bar分为两种类型Mem BAR/IO BAR。

4 Mem Base Address

1.Mem Base Address,CPU系统Memory空间给PCIe设备分配空间,CPU通过Mem指令可访问PCIe设备空间。

2.PCIe设备最多可支持 6个BAR(BAR0~BAR5),2个32位Bar构成一个64位Memory Base Address(Mem Bar)。

3.Memory Base Address 格式。

4.获取Bar Size,硬件将Bar寄存器中标识Bar Size的位固定为0,软件不可写入。

4.获取Bar Size,硬件将Bar寄存器中标识Bar Size的位固定为0,软件不可写入。

向BAR写入全1(0xFFFFFFFF),再读取其值,获取Bar Size。

向BAR写入全1(0xFFFFFFFF),再读取其值,获取Bar Size。

5 IO Base Address

1.IO Base Address,CPU系统IO空间给PCIe设备分配空间,CPU通过IO指令可访问PCIe设备空间。

2.CPU系统IO空间比较小,比如x86 IO空间为64KB。

3.PCIe IO Bar, IO Bar [31:16] Bit固定位0,IO Bar Max Size 64KB。

4.目前支持IO BAR PCIe设备极少见。

6 Summary

1.PCIe BAR定义了设备资源(如寄存器、内存缓冲区)需要在CPU系统地址空间中的映射类型Mem/IO以及需要的大小。

2.PCIe Bar指向CPU系统地址空间给PCIe设备分配的位置即地址。

3.PCIe Bar使得CPU或DMA控制器能够通过内存访问(Memory-Mapped I/O, MMIO)或端口I/O(Port I/O)与设备通信。

3.PCIe Bar使得CPU或DMA控制器能够通过内存访问(Memory-Mapped I/O, MMIO)或端口I/O(Port I/O)与设备通信。

---------------------------------------------------------

---------------------------------------------------------

文章坚持-工作中查阅可解决实际问题

您的点赞-收藏-转发-评论是我们坚持原创的动力

欢迎关注微信公众号"芯塾科技"

视频发布平台:B站/公众号/抖音,可搜索"芯塾科技"观看

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网