日志

DVT| DVT在PSS中的应用

| ||

便携式激励技术是IC验证中最热门的话题之一。一些EDA供应商已经开发了相关的工具,并与Accelera Systems Initiative合作,为它们定义一个标准的输入格式。便携式激励标准(PSS)1.0版于2018年6月发布,人们对这一方法很感兴趣。现在所有相关的商业工具都支持该标准,采用速度正在加快。

然而,在实际芯片设计中采用PSS并不是一件容易的事。PSS提供了两种输入格式,这两种格式都比传统的Systemverilog约束随机测试台抽象得多。便携式激励方法令人印象深刻的功能是由输入格式中丰富的结构驱动。学习曲线很重要,甚至专家用户也可能要经常查阅标准。本文将介绍如何应对这些挑战并加快PSS的采用。

PSS背景

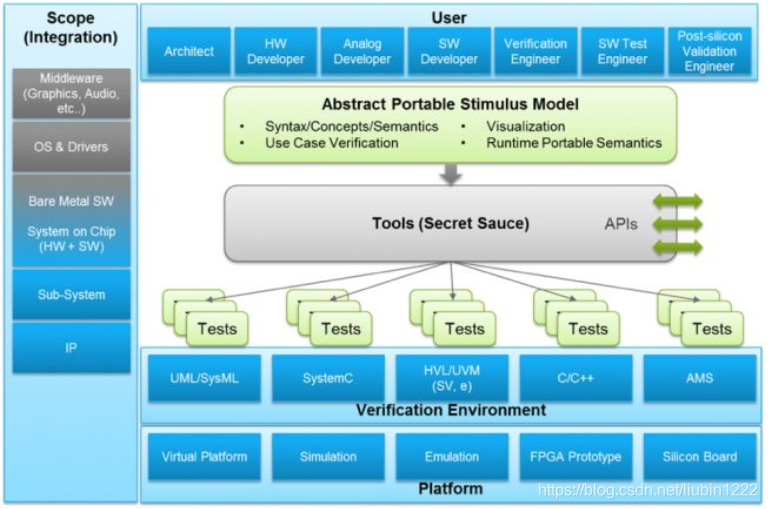

便携式激励的目标很明确:找到一种方法来编写测试,这种测试可以“垂直地”从IP块移植到子系统再移植到系统,以及“水平地”从仿真到模拟再到硅后测试。这一目标在图1中得到了很好的体现,这是Accelera在组建便携式激励工作组(PSWG)的初期开发的图表。如图所示,其思想是定义一个抽象模型,EDA工具可以从中生成适用于每个设计层次结构和每个验证平台的测试。

图1便携式激励的范围覆盖了许多目标和用户类型(Accelera)

“便携式激励”一词有误导性,因为激励不能跨平台移植。在仿真中,激励通常是由一个试验台提供的,这个试验台甚至不存在于电路内仿真或在实验室中制造的芯片。同样,由于提供激励和检查结果在不同的平台上以不同的方式进行,所以测试也不可移植。重要的是,便携式激励还包括通过在嵌入式处理器上运行测试来验证芯片的概念。

可移植性实际上存在于抽象模型中,因此商业EDA工具通过生成针对不同目标的测试来提供其与众不同的价值。例如,仿真测试可能很短,输入和输出活动频繁,而芯片内嵌入式测试可能会在引脚活动最少的情况下运行很长一段时间。PSWG的建立是为了定义抽象PSS兼容模型的格式,由芯片验证团队定义他们的需求,EDA供应商开发验证工具,以确保能够从生成的模型中高效地生成测试。

如图1所示,PSS旨在为广泛的用户提供服务,可从系统架构师到硅后验证团队。这些用户的体验和需求差异很大,因此不可能创建一种服务于所有人的格式。PSS定义了两个语义等价的格式,一个是受SystemVerilog影响的领域特定语言(DSL),另一个是C++类库。人们期望验证工程师会选择前者,而系统架构师和嵌入式程序员会选择后者。本文主要讨论DSL,因为它有独特的语法和语义。

毫无疑问,PSS非常强大,它有很多令人印象深刻的研究例程并被广泛的采用。不可否认的是它很复杂:当前的1.0a发行文档有319页。对于希望在实际项目中使用该标准的芯片团队来说,这种复杂性可能会令人望而生畏。但是现代芯片设计和验证任务涉及多种语言和格式,集成开发环境(IDE)可以减少学习时间,甚至为有经验的用户节省工作量。毫无疑问,PSS的IDE也会带来类似的好处。

IDE的价值

IDE作为很好地建立了一种简化复杂语言采用的方法的工具,已经得到了广泛的应用。IDE最初是为了帮助软件程序员开发的,而现在可以为硬件设计师和验证工程师提供IDE。它支持SystemVerilog、Verilog、Vhdl、E、C/C++、SystemC以及UPF和CPF电源意向格式。工程师可以交互地开发、测试和调试他们的代码,同时管理具有数千个设计和测试台文件的复杂项目。在众多功能中,IDE可以:

对代码执行多种类型的检查;

根据用户偏好突出显示和格式化代码;

编写代码,给出完整的设计和测试平台结构;

连接到模拟器以调试失败的验证测试用例;

为代码开发提供直观的图形用户界面。

因为IDE编译了所有的设计和验证源代码,所以它可以构建一个完整环境的内部数据库。在这个数据库中封装的功能支持远远超出传统文本编辑器的功能。IDE可以遍历深层设计和测试台层次结构,给出修复错误代码的可行方法,重构代码以提高效率和可维护性,自动完成部分输入,并为添加新代码提供模板。这些特性对于DSL模型和任何其他语言都同样有价值。

交互式PSS的开发与调试

PSS DSL可以看作是芯片设计和验证的另一种语言。虽然它能够在比大多数语言更高级的抽象级别上进行建模,但它从IDE支持中获得的好处与大多数语言基本相同。IDE编译的内部模型包含PSS信息,因此可以应用所有适用的检查和特性。其中包括在设计中引导、检测错误、建议修复、自动补全、代码模板和重构代码。

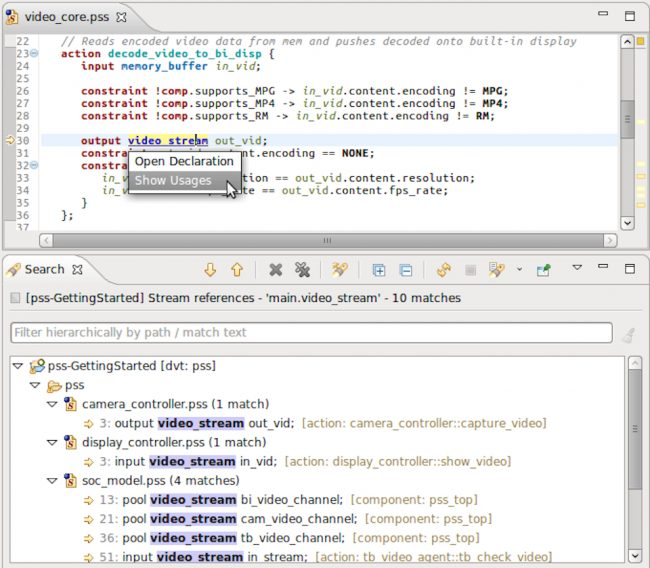

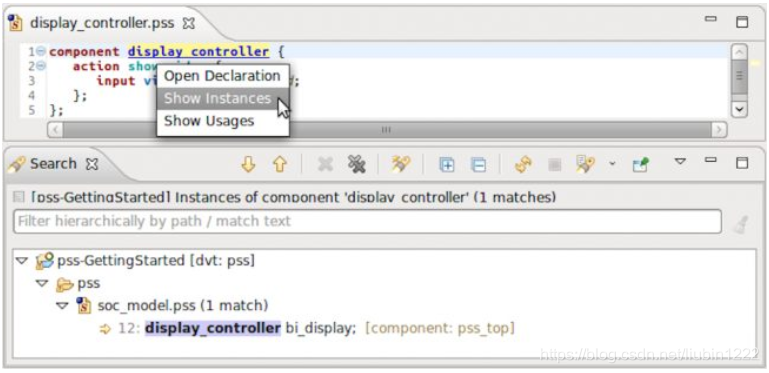

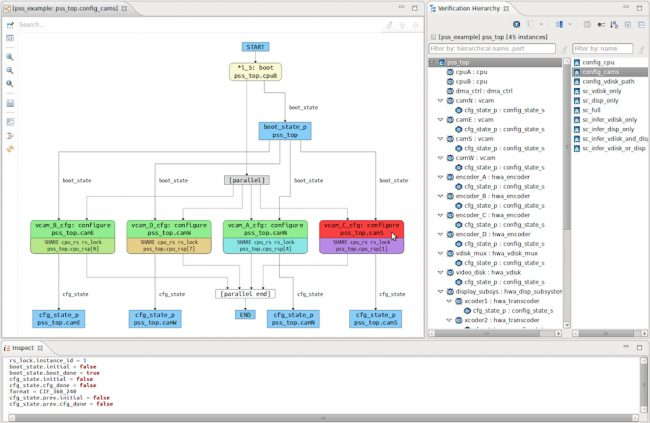

PSS模型相当大,具有很深的层次结构和许多重复的实例。与任何大型模型一样,引导也是一项挑战。搜索成百上千的文本是一件乏味的事情。由于IDE已经编译了整个设计和测试台,所以很容易跟踪所有的互连。用户可以点击任何信号并跳转到它的定义、源和目的。类似地,用户可以很容易在方法、字段、结构、操作或任何其他PSS元素的定义和用法之间切换。图2给出一个示例。类似地,图3展示了IDE,显示了PSS组件的所有实例化。这些屏幕截图和以下示例来自AMIQ EDA的设计和验证工具(DVT)Eclipse IDE。

图2 IDE可以跟踪PSS流并找到其所有用法(AMIQ EDA)

图3 IDE可以搜索并显示组件的所有实例(AMIQ EDA)

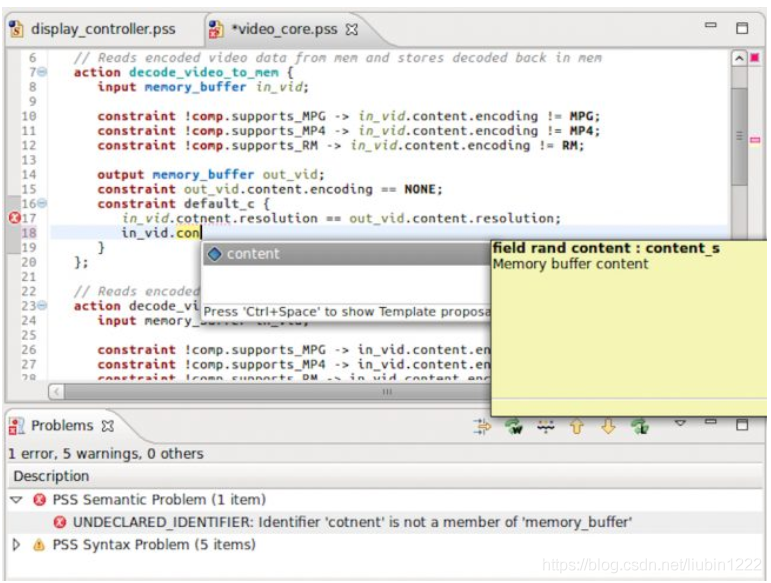

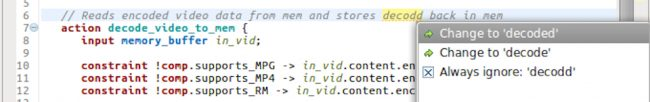

在IDE编译和分析PSS模型时,会标记语言构造中的语法错误、许多类型的语义错误以及未声明标识符名称的使用。在许多情况下,会给出一个可行的修复建议,如图4所示。图5演示了这些功能甚至扩展到了检查注释中的拼写错误。

图4 IDE可以检测命名错误并给出修复建议(AMIQ EDA)

图5 IDE可以找到拼写错误并给出修复建议(AMIQ EDA)

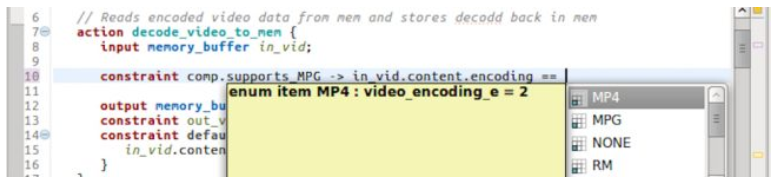

当用户输入新的DSL代码时,IDE提供了极大的帮助。模型中的语言构造和标识符都可以自动补全,从而减少出错的可能。在图6中,用户输入了部分名称,IDE提供了自动补全以供使用。然后用户继续编辑枚举类型的约束,IDE可以识别到这一点,并为自动补全提供了可用枚举值的选择。

图6 IDE可以自动补全部分名称(amiqeda)

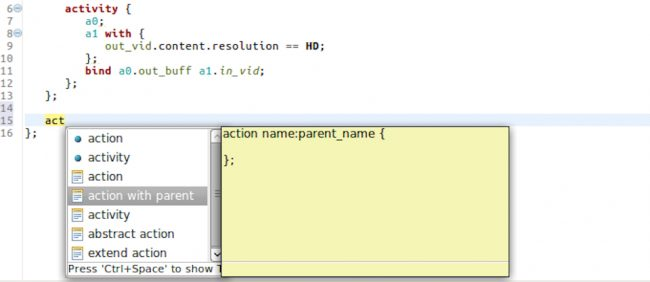

有时候,需要用户提供比从自动补全选项列表中选择所能提供的更多的信息。在这些情况下,IDE提供了一个编码模板,显示必须填写的字段。在图7中,所选选项需要指定一个操作名和一个父级名称。编码模板极大地减少了查询PSS标准以了解如何编写不熟悉结构的时间。

图7 IDE为PSS结构(AMIQEDA)提供了编码模板

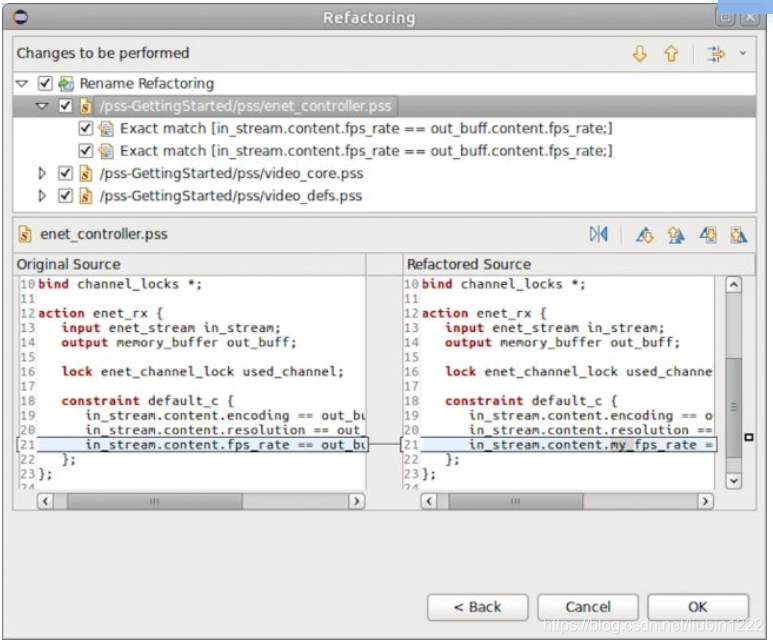

IDE还可以重构PSS代码,也就是说,在不更改其功能的情况下修改代码,包括格式化代码以符合代码风格,以及重命名元素。在图8中,IDE正在帮助用户重命名变量。此操作是自动化的,因为内部模型以及无需在文本编辑器中使用搜索即可轻松查找所有引用的方式。

图8 IDE可以重命名任何PSS元素的所有实例(AMIQ EDA)

也许IDE中最高级的PSS相关特性是场景生成和可视化。专用的EDA工具使用PSS模型为特定的设计级别、验证平台和用户生成测试。这些测试必须满足抽象的PSS规范,这需要“求解”模型以满足其约束和其他规则。IDE不会生成测试,但它可以分析PSS模型并显示满足抽象规范的场景。图9显示了一个解决方案,包括在场景中执行的操作的图形界面。

图9 IDE可以显示满足PSS模型的可能场景(AMIQ EDA)

这是一个极好的功能,因为单个PSS模型可以生成大量有效的场景。这是便携式激励提取功能的一个标志。然而,对于一个工程师来说,编写或维护一个模型来可视化可能场景的细节是很困难的。可能有多种方法可以解决模型以生成有效的场景,其中有些可能并不明显(甚至不是预期的)。此外,模型中几乎总是有许多并行线程。完整、详细场景的可视化有助于工程师确定PSS模型是否正确。如果IDE无法生成有效的场景,它将提供详细的调试信息,以帮助用户修复PSS模型。

结论

在不同的芯片项目前和后期验证阶段,通常需要多个类似的验证语言来进行硅芯片的前期验证和后期验证。在整个项目中,从同一个抽象模型生成测试的便携式激励就是为了解决这一挑战而开发的。在Accelera PSS发布之后,现在有多个EDA供应商提供了兼容的工具。虽然尚未成为主流,但采用率正在迅速增长。IDE使学习DSL变得更加容易,并且在常见操作中节省了时间,甚至对于专家来说也是如此。IDE是采用和部署PSS的重要组成部分。

作者简介

Tom Anderson是一名技术营销顾问,与多家EDA供应商合作,包括AMIQ EDA。他之前的职务包括布雷克验证系统公司(Breker Verification Systems)的市场营销副总裁、0-In设计自动化公司应用工程部副总裁、IP先锋虚拟芯片公司工程部副总裁、Cadence公司产品管理部集团总监和Synopsys公司技术营销部总监。

(加往期回顾):

。。。

原文链接:

https://www.techdesignforums.com/practice/technique/accelerating-the-adoption-of-portable-stimulus/

扫描上图二维码可直达课程页面,马上试听

往期精彩:

路科发布| 稳中带涨!25w成芯片校招薪资平均底!2020应届秋招数据全面分析!

相约今晚8点 社招转岗有顾虑?成功上岸的同学来帮你

V2Pro 2020秋M1 我对你的迷惑和选择都深以为然

V2Pro春季班普遍学撑了,秋季班7月报名你还敢来么

UVM RAL模型:用法和应用

我们准备做第二期线下培训,依旧认真且严肃

如果你突然被裁员了,你的Plan B是什么?

[彩虹糖带你入门UVM]

理解UVM-1.2到IEEE1800.2的变化,掌握这3点就够

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网