日志

SpyGlass CDC 流程深入理解 分享

热度 8| |||

SpyGlass CDC 流程深入理解(二)

------------------------------------------

版权声明:

本文作者: 烓围玮未

首发于知乎专栏:芯片设计进阶之路

转发无需授,请保留这段声明。

------------------------------------------

6. 执行CDC验证

CDC验证是指在设计中检测CDC问题。

要执行CDC验证,请执行以下步骤:

设置所需的参数(parameters)

有关SpyGlass CDC解决方案的所有参数的详细信息,请参阅Parameters in SpyGlass CDC.。

运行Goals,例如cdc_verify和cdc_verify_struct,以检测大量的CDC问题。

最初你可能会发现大量违反CDC的情况。以一种系统的方式来处理它们是很重要的,这样你就可以快速地处理一些需要考虑的问题。

下列列出了大多数重要的违例种类:

对于所有其他违规行为,请搜索SpyGlass CDC文档以查找其规则名称的违例行为。

详细的请参考 Rules in SpyGlass CDC.

6.1 未同步的跨时钟域问题 (Unsynchronized Crossings Issues)

首先,通过查看Ac_unsync01 和Ac_unsync02来检查未同步的跨时钟域问题。

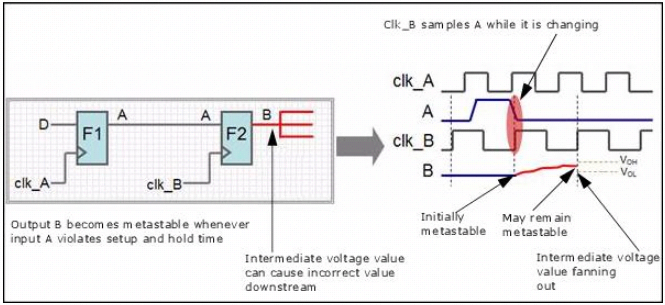

未同步就进行跨时钟域设计会产生亚稳态,这是最基本的CDC问题。

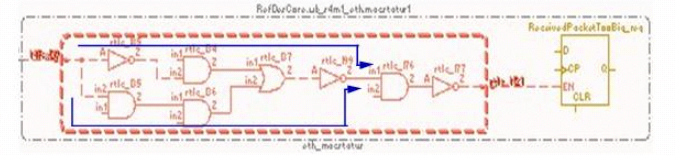

下面的例子是一种未同步信号直接跨时钟域的情况:

FIGURE 3. Unsynchronized crossing causing metastability problem

6.2 聚合问题(Convergence Issues)

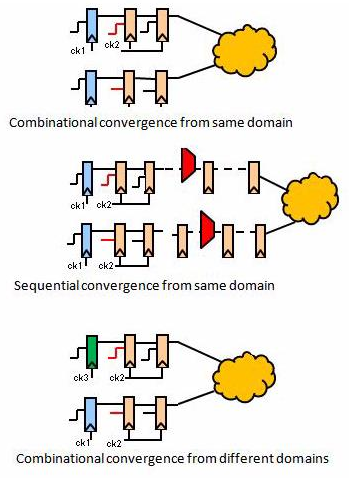

Convergence issues can occur when multiple signals cross from one domain to another but they are separately synchronized. For example, consider the following figures:

聚合问题发生在多个信号(可能是同一个时钟域也可以是不同的时钟域)从一个时钟域跨到另一个相同的时钟域,但是这些信号是分开同步的。这样你在使用这些同步过的信号的时候,就不能确定他们是不是同时有效,这样有可能就有问题。几种情况如下:

FIGURE 4. Convergence Issues

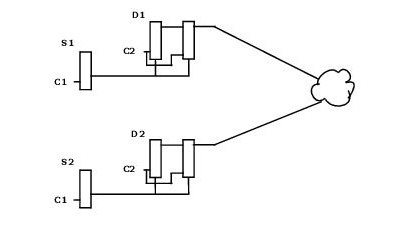

此外,当将coherence _check_type参数设置为reset时,Ac_conv规则会执行复位控制同步器的收敛性和一致性检查,如下图所示。

FIGURE 5. Convergence Issues of Reset Control Synchronizers

有关此类违规类型的信息,请参见Ac_conv01、Ac_conv02、Ac_conv03、Ac_conv04和Ac_conv05。

有关调试此类问题的信息,请参阅Debugging CDC Issues.

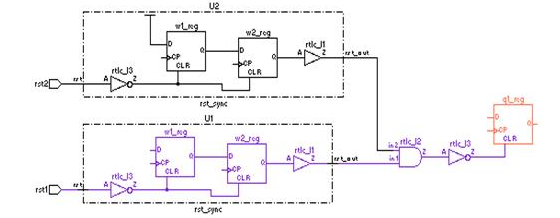

6.3 复位同步问题

对于此类问题,请检查违反Ar_*规则的情况。这些rules报告同步异步复位信号的违规行为。

由于复位通常是单比特信号,你可能希望在Ac_sync01下报告它们。但是复位的同步往往不同,比如常见的异步复位同步释放,输入是拉高的。

例如,下图显示了一个复位同步释放:

FIGURE 6. Reset that Deasserts Synchronously

有关这些违规的信息,请参见Ar_asyncdeassert01、Ar_syncdeassert01、Ar_sync01和Ar_unsync01。有关调试此类问题的信息,请参阅 Debugging CDC Issues。Ar_cross_analysis01规则执行crossing检测和同步检查,并在设计中报告reset路径中的所有时钟域crossing。用户不需要像Ar_sync规则所要求的那样在约束文件中指定reset定义。

6.4 毛刺问题

检查通过Ac_glitch*或Clock_glitch*规则报告的所有违例。

这些规则突出了容易出现毛刺的逻辑,这些逻辑可能导致与同步问题非常类似的问题。

例如,下图显示了容易出现毛刺的重新聚合的组合逻辑:

FIGURE 7. Glitch-prone reconverging combinational logic

关于这个违例更多的信息可以参考: Ac_glitch01, Ac_glitch03, Clock_glitch02, Clock_glitch03, Clock_glitch04, Clock_converge01, and Reset_sync01.

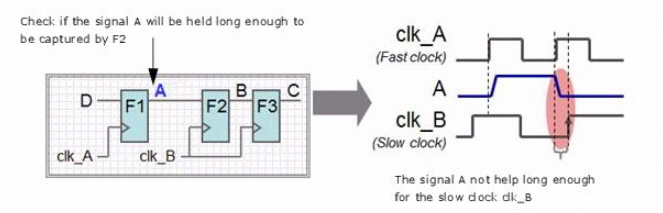

6.5 跨时钟信号宽度错误(Signal Width Errors in Synchronized Control Crossings)

请检查Ac_cdc01 rule 违例。

这种违例通常发生在信号从快时钟穿越到慢时钟,信号在慢时钟还没采样到的时候已经发生变化。

下图是信号宽度问题的例子:

FIGURE 8. Example of a signal width issue

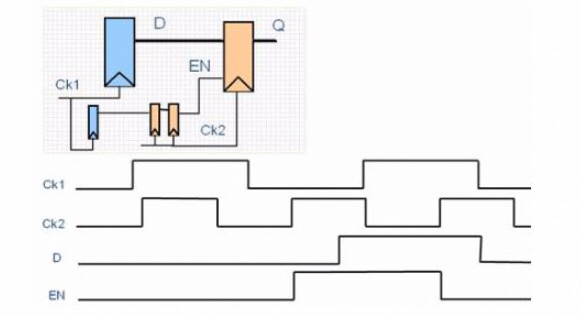

6.6 数据跨时钟的保持时间问题

请检查Ac_datahold01a 违例。

在使用同步器,但功能不正确的情况下,会出现此类违规报告的信号。考虑如下的情况:

FIGURE 9. Incorrectly Synchronized Data Crossings

上图是一种不正确的跨时钟同步器的情况。这里,数据在enable有效的时候发生了变化。

7. 调试CDC问题

在调试CDC问题之前,请保证setup是正确的。请参考Creating SpyGlass CDC Setup

在正常规模的设计上跑SpyGlass CDC,一般会有大量的违例。大部分违例是因为:

错误或者不完备的setup

配置信号,通常不应报告为CDC错误

你可以系统的,有条理的来移除这些违例,只留下一些你需要考虑的潜在的实际问题。

注意:千万不要通过waiving的方式解决CDC的问题,这样十分危险,可能wave掉了真正的CDC问题。每一条waver都必须反复check。

你可以通过以下方式来调试CDC问题:

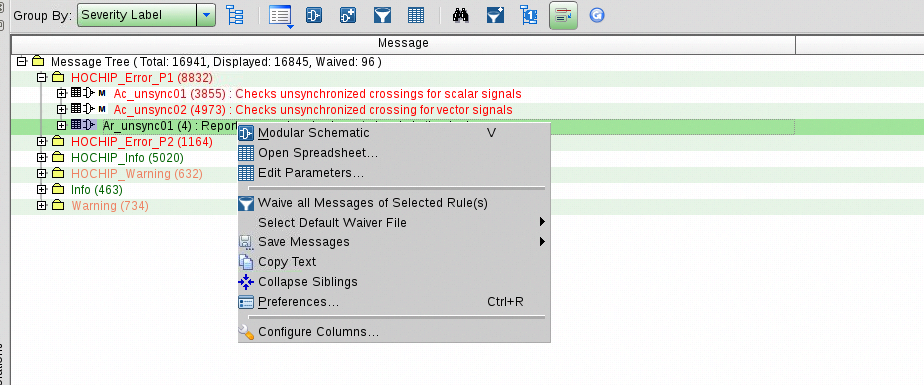

7.1 使用电子表(Using Spreadsheets)

当存在许多违规行为时,这些违规行为中的很大一部分是由一小部分的根本原因造成的。

分析它们的推荐方法是使用电子表格查看器。

执行以下步骤来使用电子表格查看器调试大部分的违规:

1. 打开电子表查看器

通过右键单击违例标题(rule的大类,比如Ar_unsync01)并从快捷菜单中选择电子表格查看器选项来打开电子表格。如下图所示

2. 筛选和排序数据

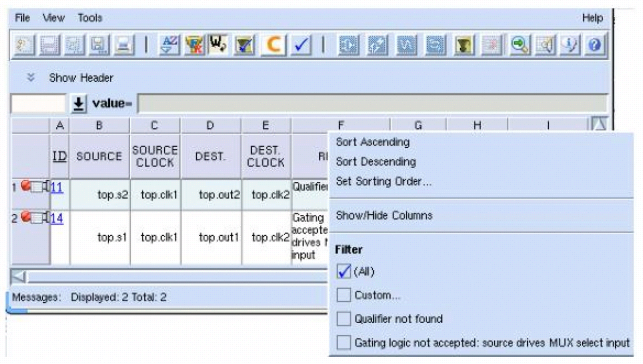

在电子表格视图中使用筛选和排序来区分共同因素和违例。要过滤或排序数据,右键单击列标题并从快捷菜单中选择一个适当的选项,如下图所示:

每一列单击可以排序,右键可以过滤:

FIGURE 10. Filtering and Sorting in the Spreadsheet

3. 检查常见原因或者来源

在电子表格中查找常见原因或常见来源。这些很可能指向一个单一的根本原因。

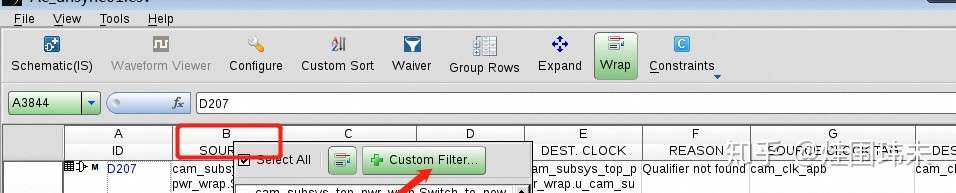

4. 根据源来进行过滤

如果您正在使用静态信号的命名方法,请在电子表格中按源名称进行筛选。比如筛选所有的配置寄存器。

例如,下图显示了如何为源指定过滤条件(_cfg):

FIGURE 11. The Custom Filter Dialo

查看过滤后的列表并解决根本原因,以消除大量违例。

7.2 使用增量示意图(Incremental Schematic)

示意图使你能够理解和隔离冲突的根本原因。

你可以查看电子表格中出现的多个相关违规的示意图。为此,请执行以下步骤:

1.通过按下<Ctrl>键盘键在电子表格中选择违规。

2.执行下列操作之一,打开增量示意图:

单击电子表格中某一行的Schematic列中的链接。

单击电子表格工具栏中的增量示意图按钮。

也可以右键直接选择Incremental Schematic

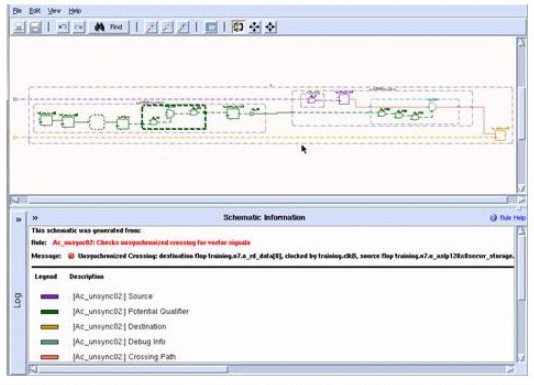

下图为增量示意图:

FIGURE 12. The Incremental Schematic Window

使用增量示意图的Tips:

使用图例了解用于标识域和限定符的颜色;

总是运行Info_Case_Analysis规则来查看常量值(constant values)在示意图中的传播;

右键单击任何net(不是pin)并选择Show Debug Data-> clock -reset选项来查看时钟和域信息。

有关详细信息,请参考Viewing Debug Data in Schematic.

可以通过双击边界边来扩展层次结构边界。

通过双击需要traced的inout/output的对象来跟踪输入和输出。

通过使用示意图中适当的右键菜单选项来跟踪输入和输出,从而跟踪到触发器、锁存器、输入、输出和模块。

7.3 在示意图中查看调试数据

在示意图中调试SpyGlass CDC解决违例时,以下信息非常有用:

clock 路径中的net的时钟域信息

reset 路径中的net的复位域信息

数据或者控制信号的时钟域信息

数据或者控制信息的准静态信息

注意:必须将enable_debug_data参数的值设置为yes,才能查看SpyGlass CDC解决方案规则的上述调试数据。

要查看示意图中的调试数据,右键单击net并从快捷菜单中选择Show debug data - >Clock-reset选项。当您选择此选项时,将出现一个子菜单,显示以下选项:

Clock

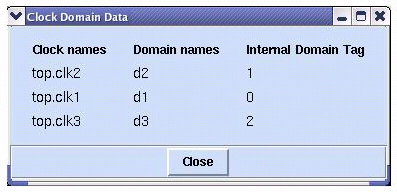

选择此选项可以查看时钟路径中出现的net上的时钟信息,如下图所示:

FIGURE 13. The Clock Domain Data Dialog

Propagate_Clocks rule计算上述信息。此选项仅对出现在设计的时钟路径中的net起作用。

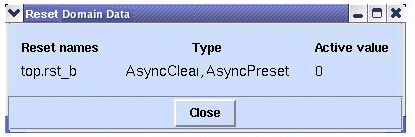

Reset

选择此选项可以查看reset路径中出现的net的reset信息,如下图所示:

FIGURE 14. The Reset Domain Data Dialog

Propagate_Resets rule计算上述信息。在上图中,Type表示复位类型,Active值表示复位源的初始值。此选项仅对在设计的reset路径中出现的net起作用。

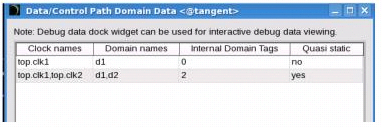

Domain in data/control paths

选择此选项,可以在设计的数据或控制路径中查看net上的时钟域信息,如下图所示:

FIGURE 15. The Data/Control Path Domain Data Dialog

在上图中,Internal Domain Tag是指在执行时钟传播时计算的内部标记,而Quasi static是指具有准静态属性的路径。数据/控制路径可以有以下类型的时钟域:

用户指定的时钟域: 这个类别包括主时钟、black box时钟和派生时钟。在这种情况下,SpyGlass会显示用户指定的时钟名称。

合并时钟域: 如果一个门上汇聚了多个时钟,则在内部创建一个合并域。在这种情况下,SpyGlass会显示用户指定的时钟列表。

虚拟时钟域: 如果一个虚拟时钟与一个块实例端口的主端口相关联,则SpyGlass将显示用户指定的虚拟时钟名。

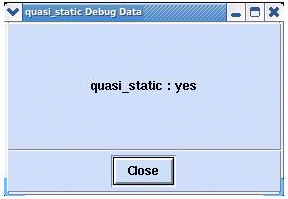

Quasi_static

选择此选项以检查net在数据或控制路径中是否是准静态的,如下图所示:

FIGURE 16. The quasi_static Debug Data Dialog

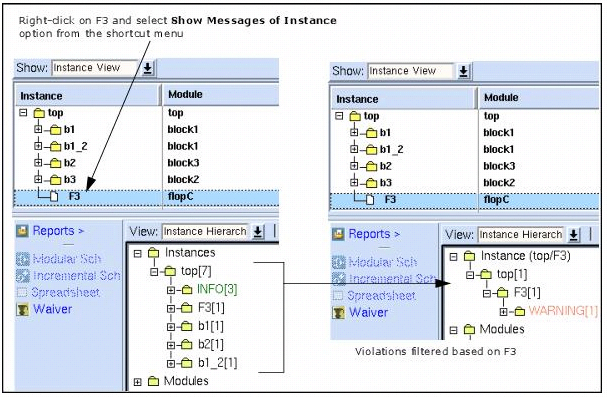

7.4 基于实例来过滤违例

在处理大型设计时,设计师会被分配特定的设计实例。在这种情况下,设计师需要关注特定实例中报告的违规情况。为了帮助设计人员快速定位特定实例上的违规,SpyGlass CDC提供了基于实例的过滤机制。在此机制中,设计人员可以基于实例筛选违规。

要基于实例过滤违规,请执行以下步骤:

1.在项目文件中指定以下命令:

set_option enable_module_based_reporting yes

2.从“视图”菜单中选择“树查看器”选项。下图展示了树查看器:

FIGURE 17. The tree viewer

确保在树查看器中选择了实例选项。

3.在instance视图中右键单击一个实例(如图17中的F3),并从快捷菜单中选择instance选项的Show Messages。

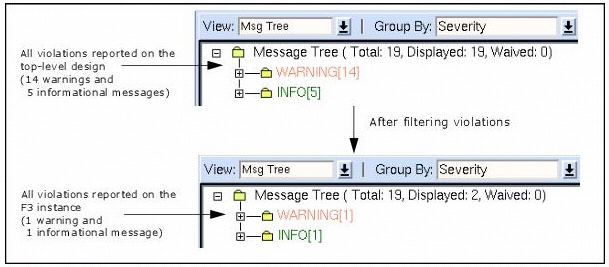

执行此步骤后,将根据F3实例过滤违规。如下图所示:

FIGURE 18. GUI view before filtering violations based on instances

注意:可以使用msg_inst_mod_report参数根据目标实例或根据公共模块过滤违规。

除了实例层次结构视图外,违例行为还可以在Msg树视图下进行过滤,如下图所示:

清理过滤器

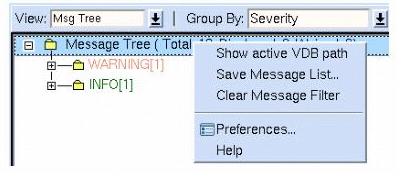

要清除过滤器并恢复出现所有违例,即顶层设计的完整视图,右键单击消息树并从快捷菜单中选择clear Message filter选项,如下图所示:

FIGURE 20. Clearing the filter

保存信息

要保存违反消息,请右键单击“消息树”窗格并选择“保存消息列表”选项。

注意:在SpyGlass Explorer中,您可以为选择的层次结构保存消息。更多信息,见SpyGlass Explorer用户指南。

7.5 解决多种CDC共同的违例问题

在大量的SpyGlass CDC违例中,大多数是以下情况:

不正确的设置

可以安全忽略的明显问题

本节描述了以下很多违例行为常见的根本原因:

Crossing发生或者结束于black box

错误的Case Analysis设置

源Flip-Flops产生静态信号

噪声

在关注rule相关的问题之前,应该首先考虑解决上述问题。解决了上述问题并重新运行SpyGlass CDC之后,您应该会看到更小、更易于管理的问题集。

注意:处理CDC问题时,千万不要通过waving。如果你采用这种方法,就有可能掩盖一个真正的问题。

7.5.1 Crossing发生或者结束于black box

SpyGlass CDC分析依据如下:

能够通过路径进行跟踪

一定程度的功能性理解

在black box的上游和下游都无法实现上述目标。

要消除这个问题,特定的约束为SpyGlass CDC提供一个部分模型,如下所述:

使用以下方法为black box的输入输出分配一个域:

对black box输出使用abstract_port约束

对black box输入使用signal_in_domain约束

使用assume_path约束对从black box输入到输出建模为直通路径。

7.5.2 错误的Case Analysis设置

检查否正确地设置了set_case_analysis约束。

例如,你可能会看到错误的原因是,所有的功能模式和所有的测试模式都是同时激活的,而实际上这些模式中的许多模式永远不会同时激活。要把test相关的信号用set_case_analysis约束。

7.5.3 源Flip-Flops产生静态信号

如果源触发器产生一个静态信号,可能不需要同步。比如说配置信号,这些信号通常在开机/启动时设置,然后不再更改。可以从芯片架构师获得关于哪些信号属于这种情况,并使用准静态约束quasi_static 来约束这些信号。

7.5.4 噪声(Noise)

在SpyGlass CDC验证的主要挑战之一是管理大量的违规。你可以通过特定的设置和设置检查步骤来降低这些“噪声”的干扰。

8. 后记

CDC检查是SOC RTL freeze之前必须要做的检查,也是最重要的检查之一。CDC检查能够提前发现功能时序仿真中发现不了的跨时钟问题,极大的减少了芯片失败的风险。系统的学习SpyGlass CDC流程,深入的理解CDC的各种问题,熟练的使用SpyGlass工具是一个资深的SOC设计人员必须具备的。

文章主要参考SpyGlass官方文档,加入自己的总结和工程经验,希望能对看到本文的芯片设计人员有所帮助。这是SpyGlass CDC 流程深入理解的第二篇文章,还有后续,请关注知乎专栏《芯片设计进阶之路》

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网