日志

在线调试工具(SIGNALTAP chipscope vivado)问题

| |||

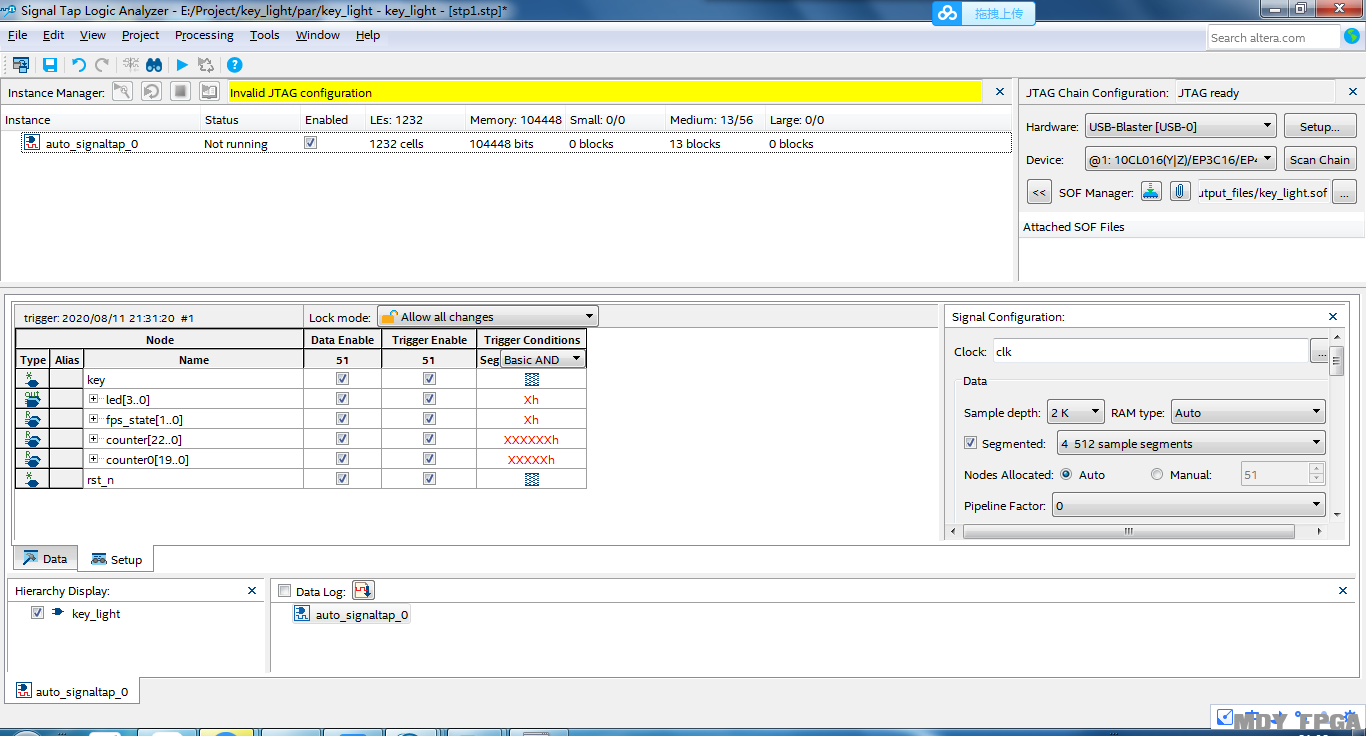

【问题1】SIGNALTAP每次后,总是出现红色提示,如下图。

答:有可能以下几种情况,请逐个进行排除。

1. 每当修改了SIGNALTAP的设置,如添加观察信号,改变深度等,需要保存后,在QUARTUS重新编译一次,生成的文件再烧写。

2. 如果烧写后,仍然出现上面情况:一定要检查sof文件生成的日期,要确保是刚刚生成的!!(这个很重要)

3. 有部分人喜欢在programmer里烧写SOF文件,然后再在SIGNALTAP里再烧写一次。这是没有必要的。请不要使用Programmer烧写。

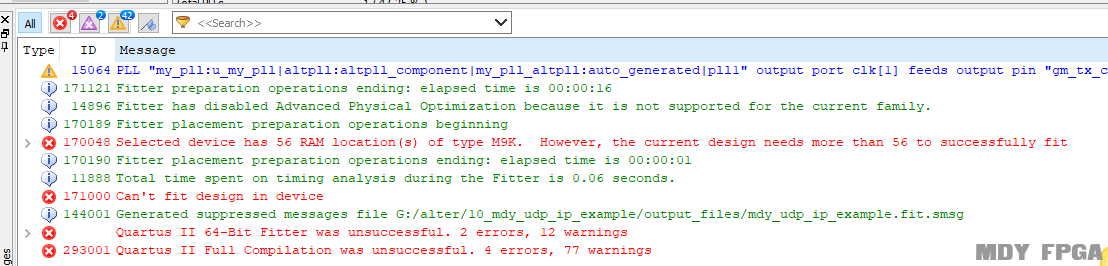

【问题2】在SIGNALTAP添加信号,编译时出现如下错误。

答:使用在线调试工具,是需要占用FPGA芯片资源的,特别是RAM资源。观察的信号越多,观察的深度越大,所需要的RAM资源就越多。

上面的问题是指,整体的资源(设计占用的资源 + 调试工具占用的资源)已经超过了芯片资源本身。

为了解决上面问题,可以将观察信号减少,或者将深度减小,再次编译试试。

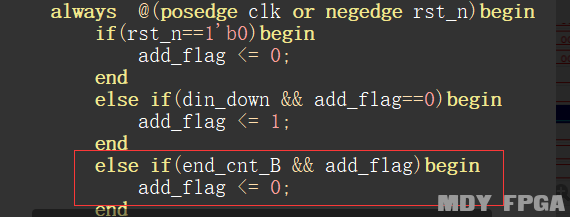

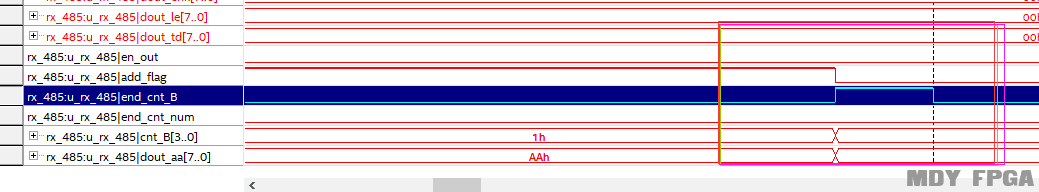

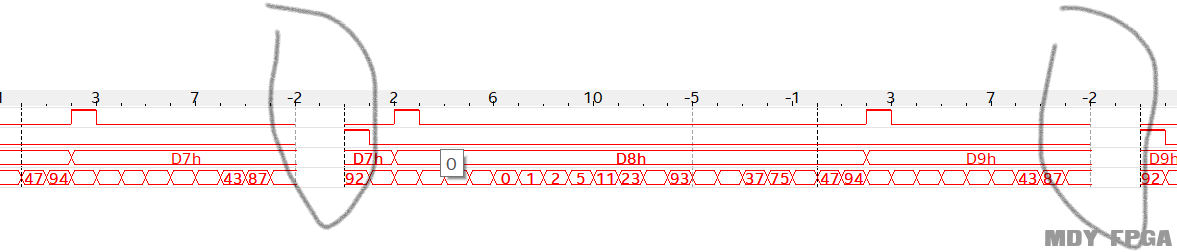

【问题3】 SIGNALTAP观察的现象和代码对不上的问题。如下图

上图中,add_flag由1变0条件是end_cnt_B=1。但观察到的是add_flag在end_cnt_B为1之前就变低了。

答:上面已经定位到某个采样点的时刻处,这已经非常好!

当定位到某个采样点,波形和代码对不上的,应该检查一下时钟:SIGNALTAP的采集时钟,必须与代码中的“clk”一致!

如果不同,就会有异常现象,看到的也不正确。

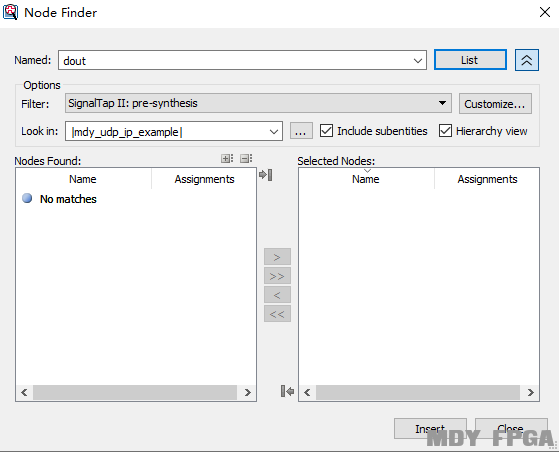

【问题4】在添加信号时,搜索框中搜索不到所需要的信号,如下图

答: 1. 搜索信号时,建议加上通配符*,即上面应该搜索“*dout*”。因为SIGNALTAP的信号名与代码中的并不相同,有时会加前缀和后缀。

2. 其实如果搜索不到,那就不要搜索,直接点击查看有没有这个信号,从而定位出是“搜索问题”,还是说“本身没有此信号”。建议多动手多思考。

3. 将“Filter”设置为“Design entry all name”选项,再搜索。 如果此窗口都没有所需要的信号,说明就是没有。

【问题5】signaltap在使用多窗口进行触发的时候,捕捉到的波形出现空白的情况,是什么原因?

答:出现这种问题一般是由于触发条件第一次成立和下一次成立之间的间隔,小于signaltap设置的一个窗口的采样深度造成的。

【问题6】使用signaltap的时候,下载完程序出现如下提示,连接设置都没有问题,怎么办?

答:一般是由于signaltap工程没有保存,点击左上角的File,选择“Save as”,另外起一个名字进行保存。

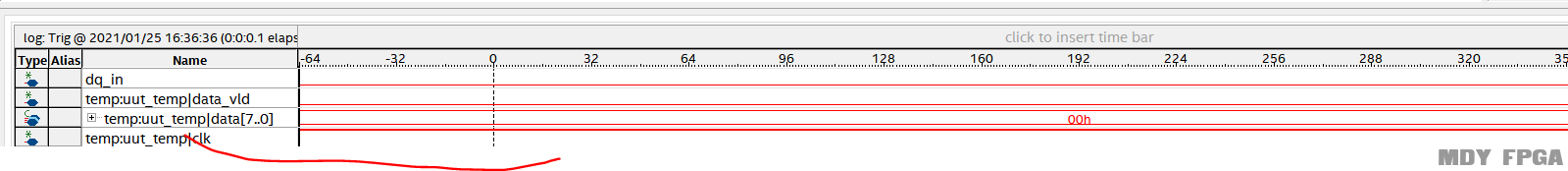

【问题7】抓取CLK信号来看,发现它一直为1,明明是有时钟的,为什么看不到变化?如下图

答:注意一下SIGNALTAP中“采样时钟”和采集信号“CLK”的关系。如果“采样时钟”就是“CLK”,想象一下会发生什么现象?

要知道SIGNATAP的原理,它是在“采样时钟”的上升沿,去采信号“CLK”。由于“采样时钟”和“CLK”是同一个信号。

当“采样时钟”上升沿的时候,同时也意味着“CLK”的上升沿,它们是同频同相的,所以你会永远采到同一个值:一直为1或者一直为0。不管运行多久时间,都不会变化的。这不是CLK没有,而是“观测”的缺陷是这样的。

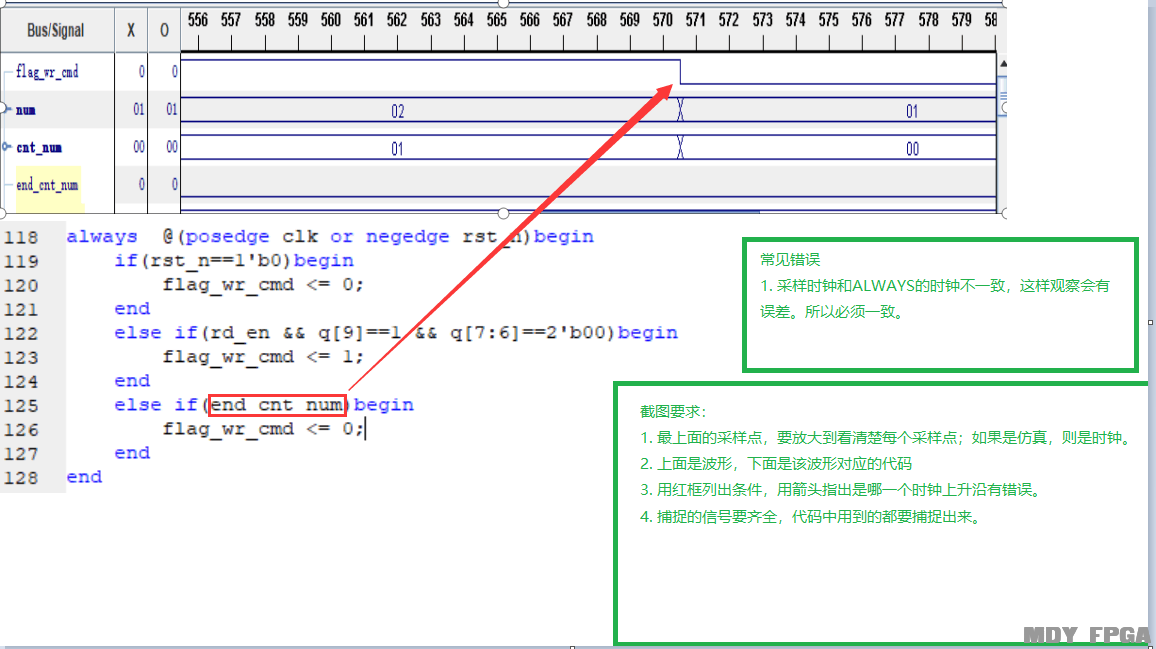

使用在线调试工具定位的技巧

【在线调试工具求助技巧】!!!在线调试工具,定位时,正确的求助方式。(请按下面方式截图)!!!!

1. 上面是在线调试工具的波形图,下面是对应的代码。

2. 哪个信号有错误,就看哪个代码。

3. 波形图要放大,能看到错误时刻"某一个采样点",如图中的最上行。

4. 波形图要将代码中出现的所有信号拉出来。

5. 波形图的信号排列顺序是:复位、条件、结果信号。

6. 哪一个时刻有错,要按上图的箭头标示出来。

7. 特别注意:在线调试工具的采样时钟,必须为该信号的工作时钟!!!

8. 如果组合逻辑信号不能观察,那可以拉组成该组合逻辑的所有信号,然后推测出结果。

9. 对于觉得上面步骤太麻烦的,我只想说一句:如果你能定位出问题,可以不这么仔细。如果你都定位不出来了,此时不就是要更加认真仔细一些吗?

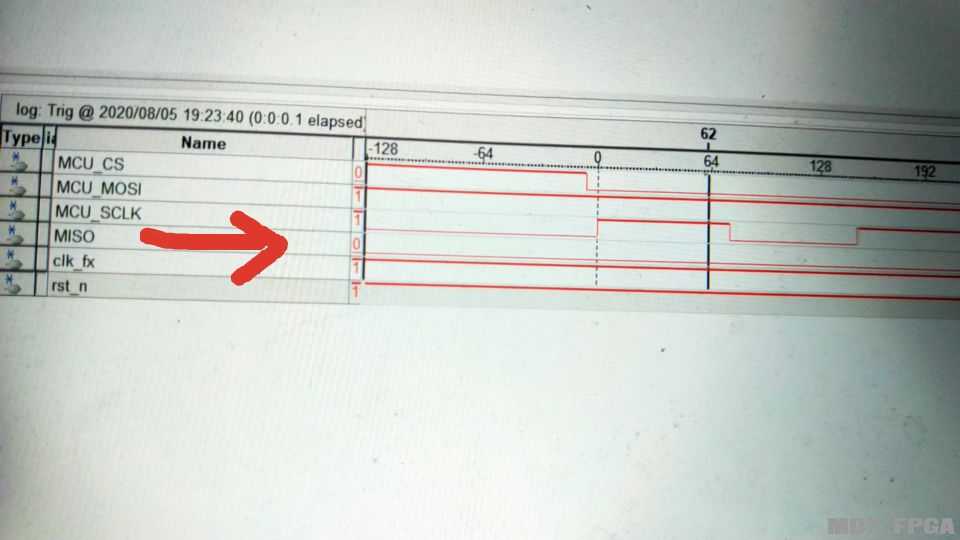

【问题8】只有波形图,但没有代码fpga仿真输出是对的,但是用signaltap显示出来就一直为零,为什么?

答:本问题,只有波形图,但没有代码。请按在线调试工具(SIGNALTAP chipscope vivado)

【问题9】在线调试工具一直处于等待触发的状态。如下图。

答:在线调试工具没有触发,只能“实实在在说明”一点:触发条件不满足! 满足了,就一定会触发!

1. 比较多错误的一点是:多个信号是相与还是相或的关系。例如上图中,其触发条件是:rst_n上升沿 并且 cnt值为5。只是rst_n上升沿了,而cnt不等于5,也不会触发。

2. 假设上图中触发条件“只有rst_n为上升沿”,如果按了按键后,还是没触发。这已经给你提示了:rst_n信号和按键之间有问题,例如管脚没配对;例化不正确等,你需要检查这些。

【问题10】SIGNALTAP添加的信号,显示的是红色,表示什么含义?

答:添加的信号,如何是红色,其可能的原因有:

1. 该信号可能一直处于固定值,例如固定为0,固定为1,或者其他数。

2. 该信号可能没有”用“,从而被优化了。这里没有用,可能是直接的,也可能是间接的。

a. 直接是指,如设计了信号A,但信号A没有作为条件来产生任何信号,那么A就是没用的,会被优化;

b. 间接是指,如设计了信号A,然后使用A作为条件产生了信号B,但B没有拿去用,那么B是无用的,间接说明A也是无用的,B和A都会被优化。

3. 该信号是组合逻辑产生的信号。组合逻辑产生的信号,在SIGNALTAP中可能不可观察,但VIVADO不存在此问题。

【问题11】在ISE,chipscope中抓取信号发现,触发位置并不是设置的触发点,稍微滞后了半个采样周期,这个是我哪儿设置的不对吗,还是本来就是这样的。

答:在线调试工具,都是一个上升沿采样一个点,所以只有第1个采样点,第2个采样点的概念,绝对没有“中间点”的概念。图上,只不过是chipscope把“这个点”标在数据中间而已,只是一个显示的方式。

【问题12】这种波形窗口能增高的吗? 要看有符号数 ADC波形,这个窗口高度太低了,看不见波形了

答:这个波形看起来小,主要是由于数值相对于位宽来说太小。例如该信号是16位的,可表示0~65535,而数值只有几十的话,那自然就很小了。从波形上看,该信号的高位都是0。所以可以只取该信号的低8位,组成一个新信号,那么波形自然就放大了。

Signaltap教程--如果同学们的问题我们帖子里面没有的请第一时间联系易老师,我们对新问题进行补充!汇总贴网址:http://www.mdy-edu.com/wentijieda/20210409/1217.html

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网