日志

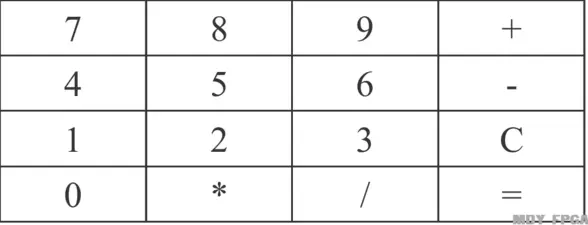

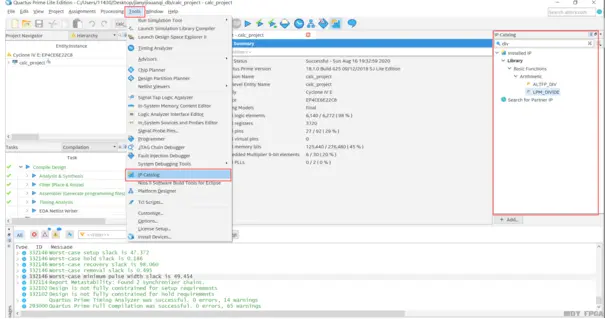

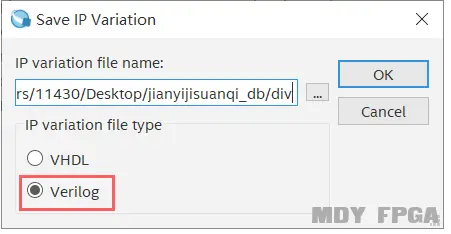

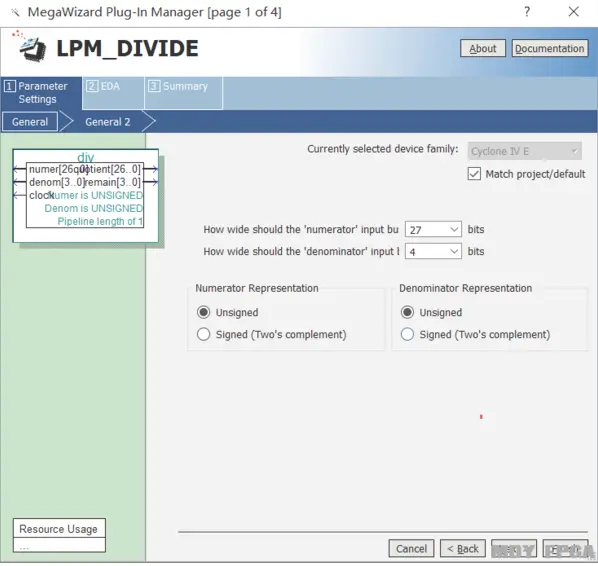

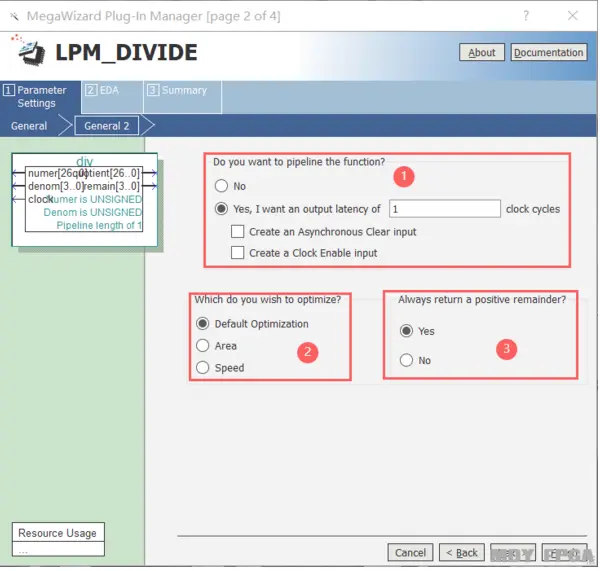

【案例】 简易计算器

| |||

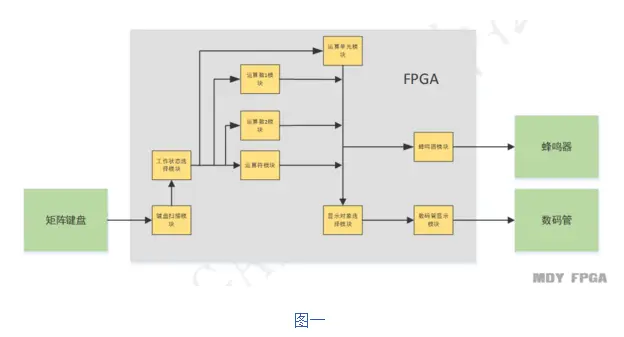

1.1.1 概述

1.1.3 系统结构框图

键盘扫描模块实现功能

工作状态选择模块实现功能

Ø 运算数1模块实现功能

Ø 运算符模块实现功能

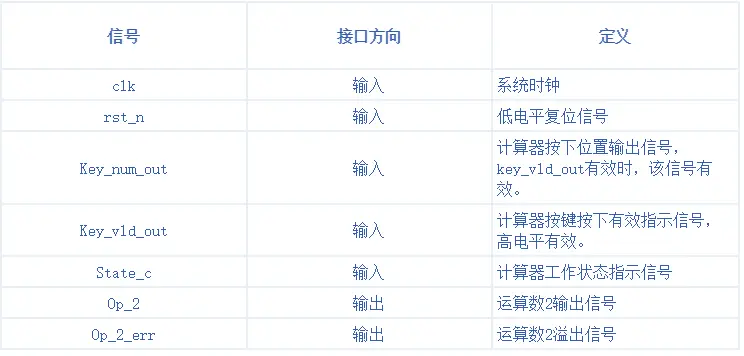

Ø 运算数2模块实现功能

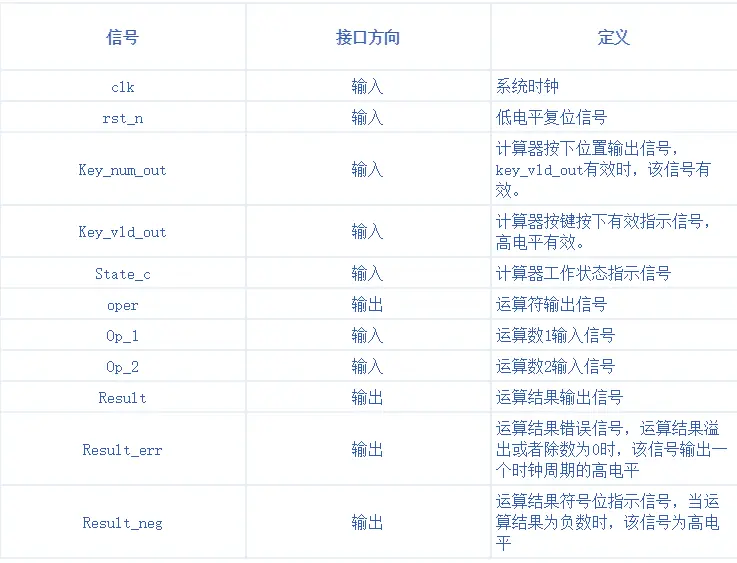

Ø 运算单元模块实现功能

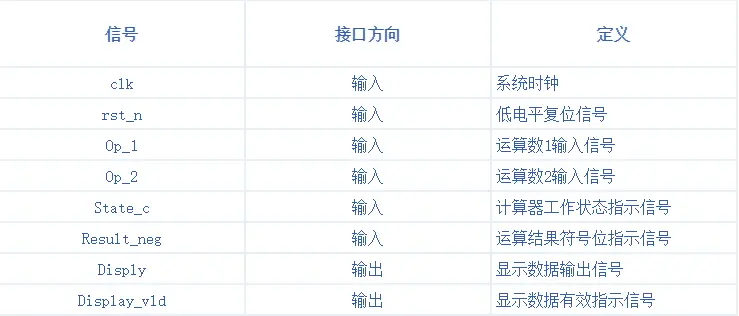

Ø 显示对象选则模块实现功能

Ø 数码管显示模块实现功能

Ø 蜂鸣器模块实现功能

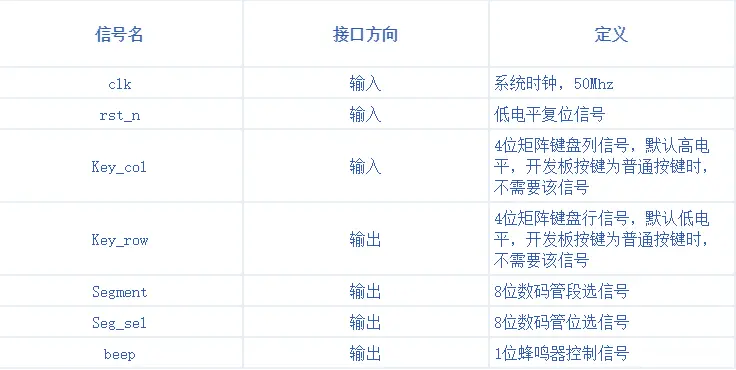

1.1.5顶层信号

1.1.6参考代码

- module calc_project(

- clk ,

- rst_n ,

- key_col ,

- key_row ,

- seg_sel ,

- segment ,

- beep

- );

- parameter KEY_WID = 4 ;

- parameter STATE_WID = 5 ;

- parameter NUM_WID = 27 ;

- parameter SEG_NUM = 8 ;

- parameter SEG_WID = 8 ;

- input clk ;

- input rst_n ;

- input [KEY_WID-1:0] key_col ;

- output [KEY_WID-1:0] key_row ;

- output [SEG_NUM-1:0] seg_sel ;

- output [SEG_WID-1:0] segment ;

- output beep ;

- wire [KEY_WID-1:0] key_num ;

- wire key_vld ;

- wire [KEY_WID-1:0] key_num_out ;

- wire [KEY_WID-1:0] key_vld_out ;

- wire [STATE_WID-1:0] state_c ;

- wire [NUM_WID-1:0] op_1 ;

- wire op_1_err ;

- wire [KEY_WID-1:0] oper ;

- wire [NUM_WID-1:0] op_2 ;

- wire op_2_err ;

- wire [NUM_WID-1:0] result ;

- wire result_err ;

- wire result_neg ;

- wire [SEG_NUM*4-1:0] display ;

- wire display_vld ;

- key_scan key_scan_prj(

- .clk (clk ) ,

- .rst_n (rst_n ) ,

- .key_col (key_col) ,

- .key_row (key_row) ,

- .key_out (key_num) ,

- .key_vld (key_vld)

- );

- work_state work_state_prj(

- .clk (clk ) ,

- .rst_n (rst_n ) ,

- .key_num (key_num ) ,

- .key_vld (key_vld ) ,

- .result_err (result_err ) ,

- .key_num_out(key_num_out) ,

- .key_vld_out(key_vld_out) ,

- .state_c (state_c )

- );

- op_1 op_1_prj(

- .clk (clk ) ,

- .rst_n (rst_n ) ,

- .key_num (key_num_out) ,

- .key_vld (key_vld_out) ,

- .state_c (state_c ) ,

- .result (result ) ,

- .op_1 (op_1 ) ,

- .op_1_err (op_1_err )

- );

- oper oper_prj(

- .clk (clk ) ,

- .rst_n (rst_n ) ,

- .key_num (key_num_out) ,

- .key_vld (key_vld_out) ,

- .state_c (state_c ) ,

- .oper (oper )

- );

- op_2 op_2_prj(

- .clk (clk ) ,

- .rst_n (rst_n ) ,

- .key_num (key_num_out) ,

- .key_vld (key_vld_out) ,

- .state_c (state_c ) ,

- .op_2 (op_2 ) ,

- .op_2_err (op_2_err )

- );

- result result_prj(

- .clk (clk ) ,

- .rst_n (rst_n ) ,

- .key_num (key_num_out) ,

- .key_vld (key_vld_out) ,

- .state_c (state_c ) ,

- .op_1 (op_1 ) ,

- .oper (oper ) ,

- .op_2 (op_2 ) ,

- .result (result ) ,

- .result_err (result_err ) ,

- .result_neg (result_neg )

- );

- display_sel display_sel_prj(

- .clk (clk ) ,

- .rst_n (rst_n ) ,

- .state_c (state_c ) ,

- .op_1 (op_1 ) ,

- .op_2 (op_2 ) ,

- .result_neg (result_neg ) ,

- .display (display ) ,

- .display_vld(display_vld)

- );

- segment segment_prj(

- .rst_n (rst_n ) ,

- .clk (clk ) ,

- .display (display ) ,

- .display_vld(display_vld) ,

- .seg_sel (seg_sel ) ,

- .segment (segment )

- );

- beep beep_prj(

- .clk (clk ) ,

- .rst_n (rst_n ) ,

- .op_1_err (op_1_err ) ,

- .op_2_err (op_2_err ) ,

- .result_err (result_err ) ,

- .beep (beep )

- );

- endmodule

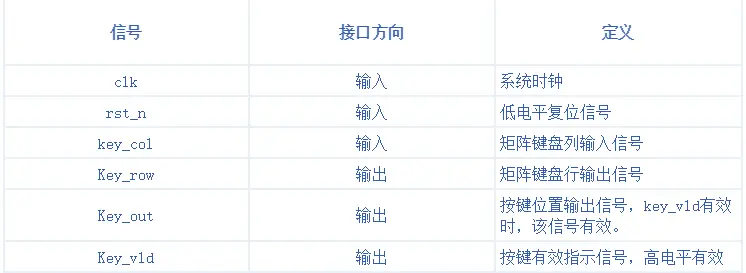

1.2 键盘扫描模块设计1.2.1接口信号

1.2.2 设计思路

1.2.3参考代码

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- key_col_ff0 <= 4'b1111;

- key_col_ff1 <= 4'b1111;

- end

- else begin

- key_col_ff0 <= key_col ;

- key_col_ff1 <= key_col_ff0;

- end

- end

- always @(posedge clk or negedge rst_n) begin

- if (rst_n==0) begin

- shake_cnt <= 0;

- end

- else if(add_shake_cnt) begin

- if(end_shake_cnt)

- shake_cnt <= 0;

- else

- shake_cnt <= shake_cnt+1 ;

- end

- end

- assign add_shake_cnt = key_col_ff1!=4'hf;

- assign end_shake_cnt = add_shake_cnt && shake_cnt == TIME_20MS-1 ;

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- state_c <= CHK_COL;

- end

- else begin

- state_c <= state_n;

- end

- end

- always @(*)begin

- case(state_c)

- CHK_COL: begin

- if(col2row_start )begin

- state_n = CHK_ROW;

- end

- else begin

- state_n = CHK_COL;

- end

- end

- CHK_ROW: begin

- if(row2del_start)begin

- state_n = DELAY;

- end

- else begin

- state_n = CHK_ROW;

- end

- end

- DELAY : begin

- if(del2wait_start)begin

- state_n = WAIT_END;

- end

- else begin

- state_n = DELAY;

- end

- end

- WAIT_END: begin

- if(wait2col_start)begin

- state_n = CHK_COL;

- end

- else begin

- state_n = WAIT_END;

- end

- end

- default: state_n = CHK_COL;

- endcase

- end

- assign col2row_start = state_c==CHK_COL && end_shake_cnt;

- assign row2del_start = state_c==CHK_ROW && row_index==3 && end_row_cnt;

- assign del2wait_start= state_c==DELAY && end_row_cnt;

- assign wait2col_start= state_c==WAIT_END && key_col_ff1==4'hf;

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- key_row <= 4'b0;

- end

- else if(state_c==CHK_ROW)begin

- key_row <= ~(1'b1 << row_index);

- end

- else begin

- key_row <= 4'b0;

- end

- end

- always @(posedge clk or negedge rst_n) begin

- if (rst_n==0) begin

- row_index <= 0;

- end

- else if(add_row_index) begin

- if(end_row_index)

- row_index <= 0;

- else

- row_index <= row_index+1 ;

- end

- else if(state_c!=CHK_ROW)begin

- row_index <= 0;

- end

- end

- assign add_row_index = state_c==CHK_ROW && end_row_cnt;

- assign end_row_index = add_row_index && row_index == 4-1 ;

- always @(posedge clk or negedge rst_n) begin

- if (rst_n==0) begin

- row_cnt <= 0;

- end

- else if(add_row_cnt) begin

- if(end_row_cnt)

- row_cnt <= 0;

- else

- row_cnt <= row_cnt+1 ;

- end

- end

- assign add_row_cnt = state_c==CHK_ROW || state_c==DELAY;

- assign end_row_cnt = add_row_cnt && row_cnt == 16-1 ;

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- key_col_get <= 0;

- end

- else if(state_c==CHK_COL && end_shake_cnt ) begin

- if(key_col_ff1==4'b1110)

- key_col_get <= 0;

- else if(key_col_ff1==4'b1101)

- key_col_get <= 1;

- else if(key_col_ff1==4'b1011)

- key_col_get <= 2;

- else

- key_col_get <= 3;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- key_out <= 0;

- end

- else if(state_c==CHK_ROW && end_row_cnt)begin

- key_out <= {row_index,key_col_get};

- end

- else begin

- key_out <= 0;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- key_vld <= 1'b0;

- end

- else if(state_c==CHK_ROW && end_row_cnt && key_col_ff1[key_col_get]==1'b0)begin

- key_vld <= 1'b1;

- end

- else begin

- key_vld <= 1'b0;

- end

- end

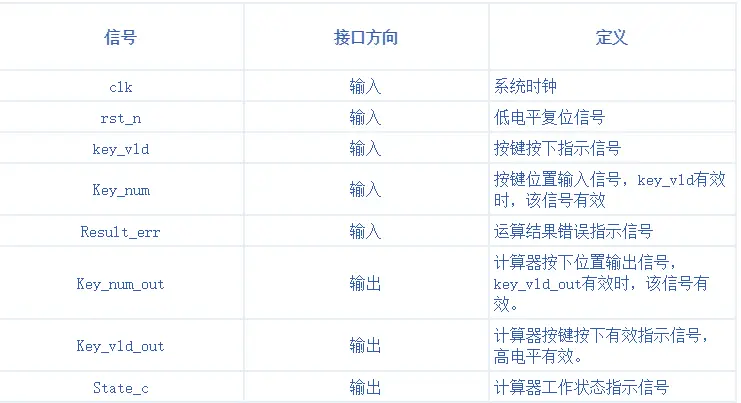

1.3 工作状态选择模块设计1.3.1接口信号

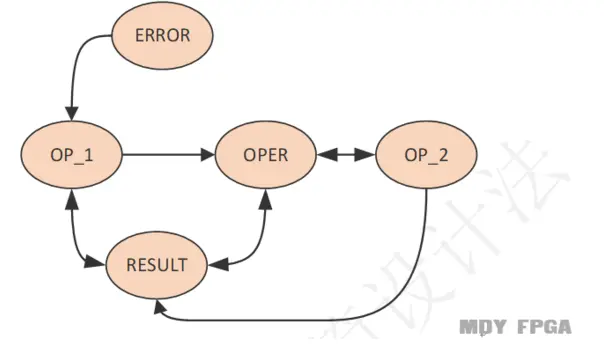

1.3.2设计思路

- always @(*)begin

- case(key_num)

- 4'd0 :key_num_chg = 4'd7 ;

- 4'd1 :key_num_chg = 4'd8 ;

- 4'd2 :key_num_chg = 4'd9 ;

- 4'd3 :key_num_chg = 4'd10 ;

- 4'd7 :key_num_chg = 4'd11 ;

- 4'd8 :key_num_chg = 4'd1 ;

- 4'd9 :key_num_chg = 4'd2 ;

- 4'd10 :key_num_chg = 4'd3 ;

- 4'd11 :key_num_chg = 4'd14 ;

- 4'd12 :key_num_chg = 4'd0 ;

- 4'd13 :key_num_chg = 4'd12 ;

- 4'd14 :key_num_chg = 4'd13 ;

- default:key_num_chg = key_num;

- endcase

- end

- assign key_num_en = (key_num_chg==0 || key_num_chg==1 || key_num_chg==2 || key_num_chg==3 || key_num_chg==4 || key_num_chg==5 || key_num_chg==6 || key_num_chg==7 || key_num_chg==8 || key_num_chg==9) && key_vld==1;

- assign key_op_en = (key_num_chg==10 || key_num_chg==11 || key_num_chg==12 || key_num_chg==13) && key_vld==1;

- assign key_cal_en = key_num_chg==15 && key_vld==1;

- assign key_back_en = key_num_chg==14 && key_vld==1;

- always @(posedge clk or negedge rst_n) begin

- if (rst_n==0) begin

- state_c <= OP_1 ;

- end

- else begin

- state_c <= state_n;

- end

- end

- always @(*) begin

- if(result_err)begin

- state_n = ERROR;

- end

- else begin

- case(state_c)

- OP_1 :begin

- if(op_12oper_start)

- state_n = OPER ;

- else if(op_12result_start)

- state_n = RESULT ;

- else

- state_n = state_c ;

- end

- OPER :begin

- if(oper2op_2_start)

- state_n = OP_2 ;

- else if(oper2result_start)

- state_n = RESULT ;

- else

- state_n = state_c ;

- end

- OP_2 :begin

- if(op_22oper_start)

- state_n = OPER ;

- else if(op_22result_start)

- state_n = RESULT ;

- else

- state_n = state_c ;

- end

- RESULT :begin

- if(result2op_1_start)

- state_n = OP_1 ;

- else if(result2oper_start)

- state_n = OPER ;

- else

- state_n = state_c ;

- end

- ERROR :begin

- if(error2op_1_start)

- state_n = OP_1 ;

- else

- state_n = state_c ;

- end

- default : state_n = OP_1 ;

- endcase

- end

- end

- assign op_12oper_start = state_c==OP_1 && key_op_en ;

- assign op_12result_start = state_c==OP_1 && key_cal_en;

- assign oper2op_2_start = state_c==OPER && key_num_en;

- assign oper2result_start = state_c==OPER && key_cal_en;

- assign op_22oper_start = state_c==OP_2 && key_op_en ;

- assign op_22result_start = state_c==OP_2 && key_cal_en;

- assign result2op_1_start = state_c==RESULT && key_num_en;

- assign result2oper_start = state_c==RESULT && key_op_en ;

- assign error2op_1_start = state_c==ERROR && key_num_en;

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- key_num_out <= 0;

- end

- else begin

- key_num_out <= key_num_chg;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- key_vld_out <= 0;

- end

- else begin

- key_vld_out <= key_vld;

- end

- end

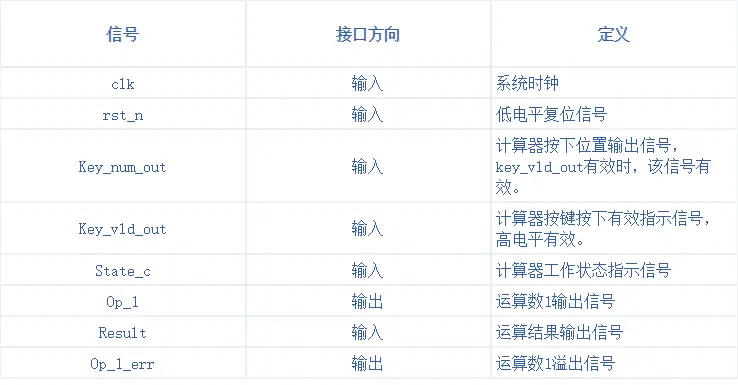

1.4 运算数1模块设计1.4.1接口信号

1.4.2设计思路

- assign key_num_en = (key_num==0 || key_num==1 || key_num==2 || key_num==3 || key_num==4 || key_num==5 || key_num==6 || key_num==7 || key_num==8 || key_num==9) && key_vld==1;

- assign key_op_en = (key_num==10 || key_num==11 || key_num==12 || key_num==13) && key_vld==1;

- assign key_cal_en = key_num==15 && key_vld==1;

- assign key_back_en = key_num==14 && key_vld==1;

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- state_c_ff <= 0;

- end

- else begin

- state_c_ff <= state_c;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- op_2 <= 0;

- end

- else if(state_c==OPER)begin

- op_2 <= 0;

- end

- else if(state_c_ff==OPER && state_c==OP_2)begin

- op_2 <= key_num;

- end

- else if(state_c==OP_2 && key_back_en==1)begin

- op_2 <= op_2 / 10;

- end

- else if(state_c==OP_2 && key_num_en==1)begin

- op_2 <= (op_2>9999999) ? op_2 : (op_2*10+key_num);

- end

- else begin

- op_2 <= op_2;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- op_2_err <= 0;

- end

- else if(state_c==OP_2 && key_num_en==1 && op_2>9999999)begin

- op_2_err <= 1'b1;

- end

- else begin

- op_2_err <= 1'b0;

- end

- end

- endmodule

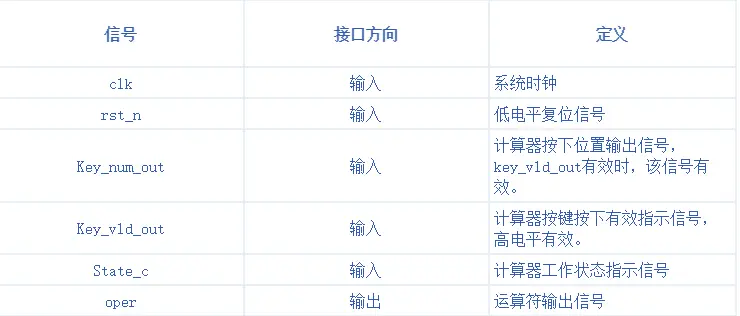

1.5 运算符模块设计1.5.1接口信号

1.5.2设计思路

1.5.3参考代码

- assign key_op_en = (key_num==10 || key_num==11 || key_num==12 || key_num==13) && key_vld==1;

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- oper <= 0;

- end

- else if(state_c==OP_1)begin

- oper <= 0;

- end

- else if(key_op_en==1)begin

- oper <= key_num;

- end

- else begin

- oper <= oper;

- end

- end

1.6 运算数2模块设计1.6.1接口信号

1.6.2设计思路

1.6.3参考代码

- assign key_num_en = (key_num==0 || key_num==1 || key_num==2 || key_num==3 || key_num==4 || key_num==5 || key_num==6 || key_num==7 || key_num==8 || key_num==9) && key_vld==1;

- assign key_op_en = (key_num==10 || key_num==11 || key_num==12 || key_num==13) && key_vld==1;

- assign key_cal_en = key_num==15 && key_vld==1;

- assign key_back_en = key_num==14 && key_vld==1;

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- state_c_ff <= 0;

- end

- else begin

- state_c_ff <= state_c;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- flag_calc <= 0;

- end

- else if(state_c==OP_1)begin

- flag_calc <= 1'b0;

- end

- else if(state_c_ff==OP_2 && state_c==OPER || state_c==RESULT)begin

- flag_calc <= 1'b1;

- end

- else begin

- flag_calc <= flag_calc;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- op_1 <= 0;

- end

- else if(state_c==ERROR)begin

- op_1 <= 10;

- end

- else if((state_c_ff==RESULT || state_c_ff==ERROR) && state_c==OP_1)begin

- op_1 <= key_num;

- end

- else if(state_c==OP_1 && key_back_en==1)begin

- op_1 <= op_1 / 10;

- end

- else if(state_c==OP_1 && key_num_en==1)begin

- op_1 <= (op_1>9999999) ? op_1 : (op_1*10+key_num);

- end

- else if(flag_calc==1)begin

- op_1 <= result;

- end

- else begin

- op_1 <= op_1;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- op_1_err <= 0;

- end

- else if(state_c==OP_1 && key_num_en==1 && op_1>9999999)begin

- op_1_err <= 1'b1;

- end

- else begin

- op_1_err <= 1'b0;

- end

- end

1.7.2设计思路

1.7.3参考代码

- assign key_op_en = (key_num==10 || key_num==11 || key_num==12 || key_num==13) && key_vld==1;

- assign key_cal_en = key_num==15 && key_vld==1;

- assign calculate = (state_c_ff==OP_2 && state_c==OPER || key_cal_en==1);

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- state_c_ff <= 0;

- end

- else begin

- state_c_ff <= state_c;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- result <= 0;

- end

- else if(calculate==1)begin

- case(oper)

- ADD:begin

- if(result_neg==0)

- result <= op_1 + op_2;

- else

- result <= (op_1>op_2) ? (op_1 - op_2) : (op_2 - op_1);

- end

- DEV:begin

- if(result_neg==0)

- result <= (op_1>op_2) ? (op_1 - op_2) : (op_2 - op_1);

- else

- result <= op_1 + op_2;

- end

- MUL:begin

- result <= op_1 * op_2;

- end

- DIV:begin

- result <= op_1 / op_2;

- end

- default:result <= op_1;

- endcase

- end

- else begin

- result <= result;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- result_neg <= 0;

- end

- else if(state_c==OP_1)begin

- result_neg <= 1'b0;

- end

- else if(state_c==ERROR)begin

- result_neg <= 1'b0;

- end

- else if(calculate==1 && oper==DEV && op_1<op_2)begin

- result_neg <= 1'b1;

- end

- else if(calculate==1 && result_neg==1 && oper==ADD && op_1<=op_2)begin

- result_neg <= 1'b0;

- end

- else if(result==0)begin

- result_neg <= 1'b0;

- end

- else begin

- result_neg <= result_neg;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- result_err <= 0;

- end

- else if(state_c==OP_1)begin

- result_err <= 1'b0;

- end

- else if((state_c_ff==OP_2 && state_c==OPER) || (key_cal_en==1 && state_c_ff!=ERROR))begin

- case(oper)

- ADD:begin

- if(result_neg==0)

- result_err <= (op_1+op_2)>9999_9999 ? 1'b1 : 1'b0;

- else

- result_err <= 1'b0;

- end

- DEV:begin

- if(result_neg==1)

- result_err <= (op_1+op_2)>999_9999 ? 1'b1 : 1'b0;

- else if(op_2>op_1)

- result_err <= (op_2-op_1)>999_9999 ? 1'b1 : 1'b0;

- else

- result_err <= 1'b0;

- end

- MUL:begin

- if(result_neg==1)

- result_err <= (op_1*op_2)>999_9999 ? 1'b1 : 1'b0;

- else

- result_err <= (op_1*op_2)>9999_9999 ? 1'b1 : 1'b0;

- end

- DIV:begin

- if(op_2==0)

- result_err <= 1'b1;

- else

- result_err <= 1'b0;

- end

- default:result_err <= 1'b0;

- endcase

- end

- else begin

- result_err <= 1'b0;

- end

- end

1.8 显示对象选择模块设计1.8.1接口信号

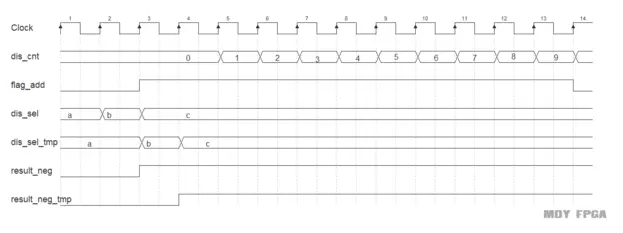

1.8.2设计思路

1.8.3参考代码

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- result_neg_tmp <= 0;

- end

- else begin

- result_neg_tmp <= result_neg;

- end

- end

- always @(*)begin

- if(state_c==OP_2)begin

- dis_sel = op_2;

- end

- else begin

- dis_sel = op_1;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- dis_sel_tmp <= 0;

- end

- else begin

- dis_sel_tmp <= dis_sel;

- end

- end

- div div_prj(

- .clock (clk ) ,

- .numer (dis_tmp ) ,

- .denom (10 ) ,

- .quotient (div_quo ) ,

- .remain (div_rem )

- );

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- flag_add <= 0;

- end

- else if(dis_sel!=dis_sel_tmp || result_neg!=result_neg_tmp)begin

- flag_add <= 1;

- end

- else if(end_dis_cnt)begin

- flag_add <= 0;

- end

- end

- always @(posedge clk or negedge rst_n) begin

- if (rst_n==0) begin

- dis_cnt <= 0;

- end

- else if(add_dis_cnt) begin

- if(end_dis_cnt)

- dis_cnt <= 0;

- else

- dis_cnt <= dis_cnt+1 ;

- end

- end

- assign add_dis_cnt = flag_add && (dis_sel==dis_sel_tmp && result_neg==result_neg_tmp);

- assign end_dis_cnt = add_dis_cnt && dis_cnt == 10-1 ;

- assign dis_tmp = add_dis_cnt && dis_cnt==1 ? dis_sel : div_quo;

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- display <= 4'b0;

- end

- else if(state_c==ERROR)begin

- display[4*(dis_cnt)-1 -:4] <= 4'b1111;

- end

- else if(end_dis_cnt && result_neg==1 && state_c!=OP_2)begin

- display[31:28] <= 4'b1010;

- end

- else begin

- display[4*(dis_cnt-1)-1 -:4] <= div_rem;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- display_vld <= 0;

- end

- else begin

- display_vld <= (dis_cnt==0 && (dis_sel==dis_sel_tmp)) ? 1'b1 : 1'b0;

- end

- end

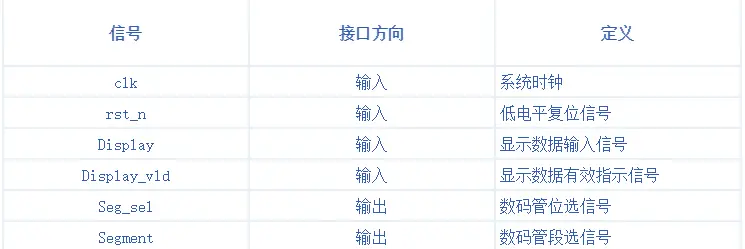

1.9 数码管显示模块设计1.9.1接口信号

1.9.2设计思路

1.9.3参考代码

- always @(posedge clk or negedge rst_n) begin

- if (rst_n==0) begin

- count_20us <= 0;

- end

- else if(add_count_20us) begin

- if(end_count_20us)

- count_20us <= 0;

- else

- count_20us <= count_20us+1 ;

- end

- end

- assign add_count_20us = 1;

- assign end_count_20us = add_count_20us && count_20us == TIME_20US-1 ;

- always @(posedge clk or negedge rst_n) begin

- if (rst_n==0) begin

- sel_cnt <= 0;

- end

- else if(add_sel_cnt) begin

- if(end_sel_cnt)

- sel_cnt <= 0;

- else

- sel_cnt <= sel_cnt+1 ;

- end

- end

- assign add_sel_cnt = end_count_20us;

- assign end_sel_cnt = add_sel_cnt && sel_cnt == SEG_NUM-1 ;

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- seg_sel <= {SEG_NUM{1'b1}};

- end

- else begin

- seg_sel <= ~(1'b1 << sel_cnt);

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- display_ff0 <= 0;

- end

- else begin

- for(ii=0;ii<SEG_NUM;ii=ii+1)begin

- if(display_vld==1)begin

- display_ff0[(ii+1)*4-1 -:4] <= display[(ii+1)*4-1 -:4];

- end

- else begin

- display_ff0[(ii+1)*4-1 -:4] <= display_ff0[(ii+1)*4-1 -:4];

- end

- end

- end

- end

- always @(*)begin

- seg_tmp = display_ff0[(sel_cnt+1)*4-1 -:4];

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- segment <= NUM_0;

- end

- else begin

- case(seg_tmp)

- 0 :segment <=NUM_0 ;

- 1 :segment <=NUM_1 ;

- 2 :segment <=NUM_2 ;

- 3 :segment <=NUM_3 ;

- 4 :segment <=NUM_4 ;

- 5 :segment <=NUM_5 ;

- 6 :segment <=NUM_6 ;

- 7 :segment <=NUM_7 ;

- 8 :segment <=NUM_8 ;

- 9 :segment <=NUM_9 ;

- 10:segment <=NUM_10 ;

- default:segment <= NUM_ERR;

- endcase

- end

- end

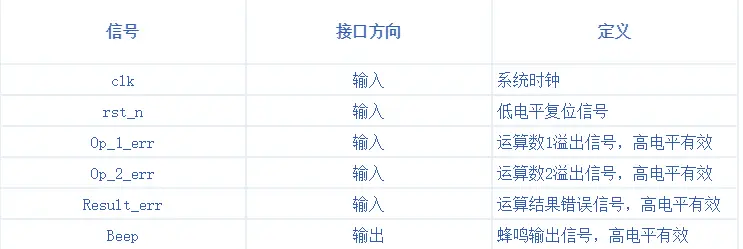

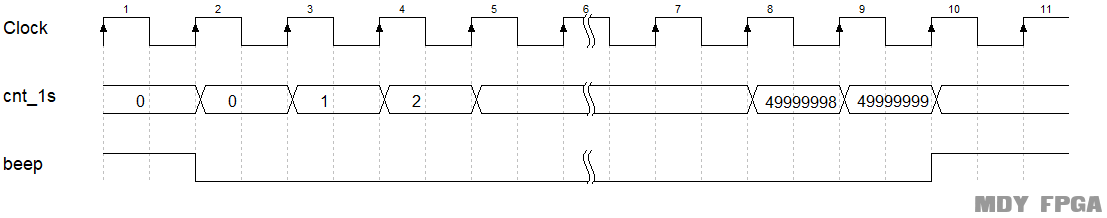

1.10 蜂鸣器模块设计1.10.1接口信号

1.10.2设计思路

- always @(posedge clk or negedge rst_n) begin

- if (rst_n==0) begin

- cnt_1s <= 0;

- end

- else if(add_cnt_1s) begin

- if(end_cnt_1s)

- cnt_1s <= 0;

- else

- cnt_1s <= cnt_1s+1 ;

- end

- end

- assign add_cnt_1s = beep==0;

- assign end_cnt_1s = add_cnt_1s && cnt_1s == CNT_1S-1 ;

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- beep <= 1'b1;

- end

- else if(op_1_err || op_2_err || result_err)begin

- beep <= 1'b0;

- end

- else if(end_cnt_1s)begin

- beep <= 1'b1;

- end

- end

1.11 效果和总结

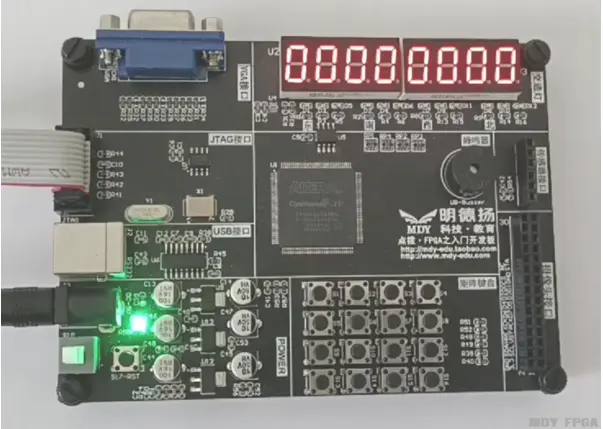

1.11.1db603开发板

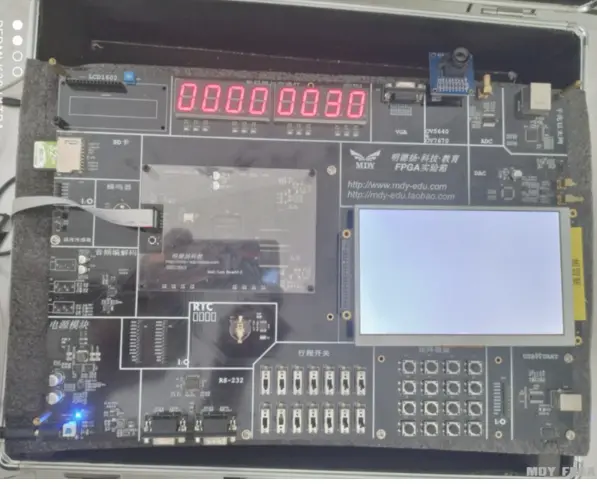

1.11.2ms980试验箱

MP801开发板——千兆网、ADDA、大容量SDRAM等,学习和项目需求一步到位。网络培训班——不管时间和空间,明德扬随时在你身边,助你快速学习FPGA。周末培训班——明天的你会感激现在的努力进取,升职加薪明德扬来助你。就业培训班——七大企业级项目实训,获得丰富的项目经验,高薪就业。专题课程——高手修炼课:提升设计能力;实用调试技巧课:提升定位和解决问题能力;fifo架构设计课:助你快速成为架构设计师;时序约束、数字信号处理、PCIE、综合项目实践课等你来选。项目承接——承接企业FPGA研发项目。人才服务——提供人才推荐、人才代培、人才派遣等服务。

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网