日志

PFDCP-PLL中模块噪声仿真设置说明

热度 4| ||

2025/08/20查找资料总结

pss+pnoise设置说明

| pss | |

shooting harmonic balance | shooting是基于时域的仿真,适用于非线性电路; harmonic balance是基于频域的仿真,适用于轻微非线性电路; shooting的特点是收敛性好,harmonic balance的特点是仿真速度快,若选择harmonic balance,一般直接用hb+hbnoise PFDCP-PLL中,PFD+CP/NDIV/REFBUF直接选shooting,VCO可以用shooting,若用了EMX抽取,用hb仿真更容易收敛 |

| Beat Frequency | 决定pss shooting阶段的仿真时间,对应仿真电路中所有周期信号的最小公倍数,选择auto calculate可以由仿真器自动计算 PFDCP-PLL中,PFD+CP/REFBUF选择auto calculate,NDIV手动填写NDIV输出频率,VCO手动填写靠近VCO振荡频率的值 |

| Oversample Factor | harmonic balance中一个选项,用于控制每个基波周期内的时间采样点数,配置越大,精度越高,仿真速度越慢;足够高的时间分辨率对于准确捕获快速变化的波形至关重要,尤其是包含陡峭边沿的波形(例如时钟信号),如果采样点不足,就无法准确描述这些快速跳变,从而导致仿真精度下降,甚至收敛困难 在VCO仿真中,一般设置为1,可以配置更大的值对比结果,折中精度和速度 |

| Output harmonics | 一般选择默认的Number of harmonics(谐波数量) 谐波数量不仅会影响pss shooting仿真的精度,还会影响pnoise等小信号计算; 谐波数量设置越大,仿真结果越准确,但是速度也越慢。 PFDCP-PLL中,一般会设置10~50,仿真初期对比不同值对结果影响,来确定用什么值更合理 |

| Accuracy Defaults | 仿真精度设置,这个也受环境精度设置影响 PFDCP-PLL中,一般会设置conservative,遇到收敛问题和仿真速度问题,在结果变化不大时会设置moderate和liberal |

| Transient-Aided Opitons | 瞬态设置,在pss仿真前跑一段tran来确定shooting的initial state PFDCP-PLL中,一般会设置,tstab时间设置需要保证仿真电路已稳定,Detect Steady State根据情况选择 |

| Oscillator | 仿真XO/VCO振荡器类型电路需要进行配置 |

| pnoise | |

| Sweeptype | relative or absolute:relative用于载波附近的相位噪声分析,是相对载波频率的频偏,可设置0/1/1.5/2/...,结果一般是dBc/Hz;absolute是绝对频率,结果一般是dBV/Hz或者dBA/Hz PFDCP-PLL中,PFD+CP设置absolute,输出dBA/Hz结果(也有地方说可以用relative=0,未验证);其他模块选择relative,一般情况下relative=1(NDIV或者分频类型电路,Beat Frequency需要配置仿真电路中的最小基频频率,而观察的输出可能是基频的倍数,就需要配置相应的relative值,例如基频是10MHz,观察的节点是30M,relative配置3) |

| Noise Type | 新版本里面下拉选项只有timeaverage和sampled(jitter)两个选项:timeaverage仿真的是一个周期内噪声的平均值;sampled(jitter)会计算大信号周期中某一时刻或者某些时刻的采样噪声,这些时刻由Timing Event决定。 PFDCP-PLL中,PFD+CP/VCO用timeaverage;REFBUF/NDIV等时钟类信号电路用sampled(jitter),Timing Event选择Edge Crossing,这个设置完成后需要点击Add,不然无效。 |

| Noise Type: Sampled(jitter) |

|

ps:对于配置更准确的说明参考virtuoso spectre的文档

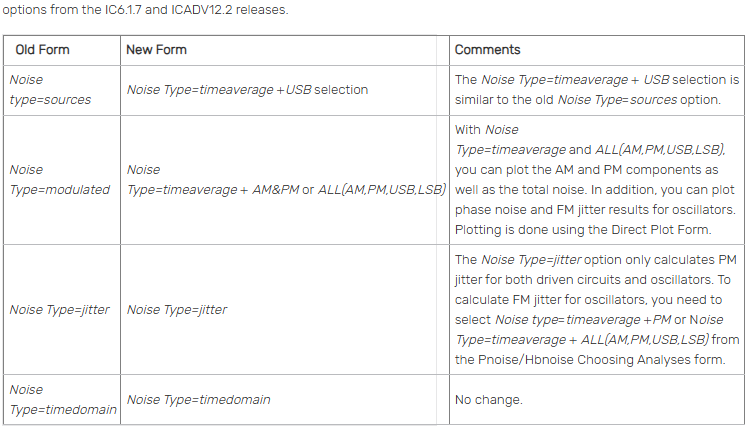

pnoise中Noise Type版本变化

最早:sources/modulated/jitter/timedomain

IC6.1.7 and ICADV12.2后:timeaverage/jitter/timedomain

ICADV12.3ISR21后:timeaverage/sampled(jitter)

参考:

【模拟IC学习笔记】 PSS和Pnoise仿真_pss仿真-CSDN博客

phase noise仿真中,pnoise里noise type的设置问题 - 第4页 - Analog/RF IC 设计讨论 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

振荡器的相位噪声仿真,pss和hb/hbnoise仿真设置 - wuhan9719的日志 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

Oversample Factor的确定 - 研究生笑笑的日志 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网