日志

时钟设计优化实战

| ||

1、时钟设计,芯片性能的节拍器

在现代 IC 设计中,时钟网络的优化是实现高性能、高可靠性和低功耗的关键。本文聚焦四大核心技术:CTS 优化、DCD 最小化、时钟门控和时钟域交叉(CDC),带你深入理解并掌握先进的时钟设计策略。

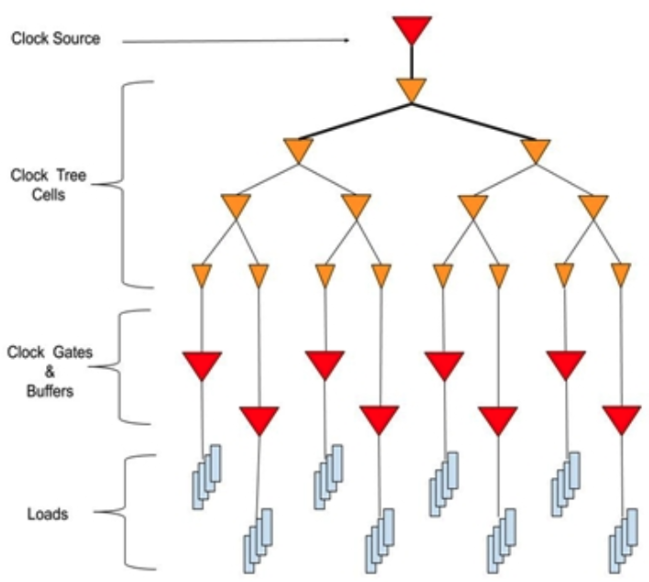

下图展示了典型的时钟树结构(Clock Tree),用于平衡时钟延迟与偏斜。

2、核心技术详解

I. CTS 优化:消除时序违例的第一步

时钟树综合(CTS) 是物理设计中构建平衡时钟网络的关键步骤,通过插入缓冲器和反相器,实现最小时钟偏斜与延迟(skew + insertion delay)。例如,当启用全局布线(global routing)而非虚拟路由预测时,可以显著提升时序精度与一致性。

而“有用偏斜(useful skew)”技术则可通过人为调整时钟到达路径,缓解 setup/hold 违例。在实测中,通过 CTS 设置与命令(如 opt_useful_skew)的合理应用,有效优化了时序性能。

II. 降低 DCD:拥抱高密度设计的挑战

占空比失真(DCD) 是高频深布线设计中常见的问题,源于上升沿与下降沿的延迟差异,尤其在 7nm 节点后更加明显。

解决之道之一是采用 Infinisim 的 ClockEdge 工具,其通过 SPICE 级别仿真,覆盖百万门电路网络,实现高精度寄生分析和 DCD 检测,挖掘传统 STA 无法发现的潜在问题,提升签核信心。

III. 时钟门控:动态关断,拥抱低功耗

时钟门控(Clock Gating) 是数字设计中最广泛采用的动态功耗优化技术之一,通过停止时钟信号传导至空闲模块,显著降低切换功耗。

其中 顺序时钟门控(Sequential Clock Gating) 在多个时钟周期基础上进行区域判断,相较于组合门控更为精确,可节省高达 30% 时钟功耗。但手工设计复杂,容易出错—工具如 Calypto PowerPro 可自动推断并验证时序逻辑,保障设计高效可靠。

IV. CDC 验证:多域交叉的安全机制

在多时钟域 SoC 中,信号跨域需防止亚稳态、毛刺和数据一致性问题。分层时钟域交叉(Hierarchical CDC) 验证方法,如底向上与顶向下混合策略,可及早识别异步边界问题。

Motellus 的 Maestro 技术进一步优化了多速率通信路径,减少 CDC fifo 使用与重定时 flops,提高 PPA 效率与设计健壮性。

3、为什么选择 EDA Academy 深入学习?

· 课程前沿全面:无论是 CTS 调优、DCD 分析、时钟门控策略,还是 CDC 验证流程,EDA Academy(www.eda-academy.com) 都提供最新、实战驱动的系统课程,让你完整掌握时钟设计要点。

· 灵活身份切换:你既可以作为学员深造,也可注册导师,分享经验提升自我。

· 免费 Newsletter 订阅:只需邮箱注册,即可定期获得时序设计新技术、工具评测和实战案例。

· 销售联盟回报机制:加入推广课程的销售联盟,推荐即有 20%–50% 佣金,让你学有所值还能收获收益。

通过优化 CTS、消减 DCD、应用高效时钟门控、以及强化 CDC 验证,设计师能够显著提升 IC 时序性能、节省动态功耗、提升设计鲁棒性。而 EDA Academy 则是你深化这一核心领域、扩展能力与职业价值的最佳平台。欢迎访问www.eda-academy.com,开启你的时钟设计实战成长之旅!

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网