日志

逻辑设计新范式

| ||

1、跨越传统的逻辑优化之路

在数字设计领域,Pass-Transistor Logic(PTL)与 FPGA 中的 Look-Up Tables(LUT)正成为追求高效、低功耗 IC 的重要基础。本文将深入解析这两种技术,助您掌握数字逻辑设计的前沿思维。

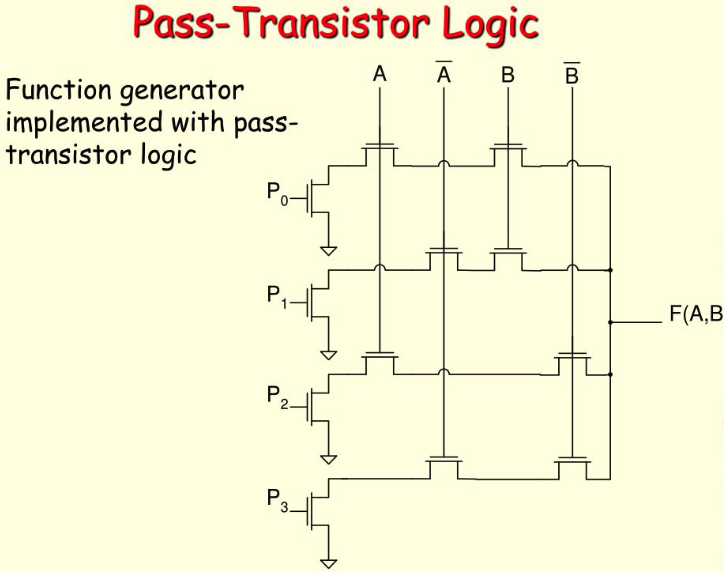

2、Pass-Transistor Logic(PTL)精要

I. 什么是 PTL?

PTL 利用晶体管作为“传输开关”直接传递信号,而非通过传统 CMOS 门。这种设计极大降低了晶体管数量与功耗开销,尤其适合追求高效和资源节省的场景。

II. 应用示例:XOR 与 AND 逻辑优化

经典 CMOS 实现一个 XOR 门可能需 12 个晶体管,而 PTL 只需约 6 个晶体管便能实现同等功能。通过传输门(transmission gate)与反相器的巧妙布局,即可构建更高效的逻辑结构。

III. 时序电路中的应用:PTL gated latch

PTL 同样可用于构建时序组件,如 gated SR latch,相比于传统 CMOS 实现,其晶体管数更少、面积更小,适合用于内存与寄存器结构中。

3、FPGA 中的 LUT:灵活构建的逻辑核心

I. LUT 的工作原理

在 FPGA 中,LUT 本质上是一个存储了布尔函数真值表的小型 SRAM,加上多路选择器(Mux)。输入变量作为地址选择 SRAM 单元中的输出位。

II. 灵活实现复杂函数

如要实现一个 4 输入的逻辑函数,且 FPGA LUT 只有 3 输入,那么可以采用多 LUT 配合选择器(Mux)实现的层级组合方式,既节省资源又保留灵活性。

III. 典型用途示例

通过 LUT 存储加法器或其它算术组合函数的真值表,FPGA 可以利用 LUT 快速响应,实现全加器、逻辑运算等复杂模块。

4、PTL + LUT:融合优势的完整案例解析

设想:在 FPGA 上实现一个低功耗、面积受限的低通滤波器。

I. 系数计算逻辑用 PTL 实现

对乘法与加法等关键路径逻辑,使用 PTL 可以显著减少晶体管数量和功耗。

II. 中间数据与查找任务用 LUT 完成

预先计算好的系数值与中间逻辑结果存入 LUT,利用低延迟存储机制快速调取,降低计算复杂度。

III. 整体优化

PTL 承担延迟关键路径集合逻辑,LUT 完成非关键路径值存取——二者组合实现最优时间延迟与功耗比。

5、为何选择 EDA Academy 深入学习?

I. 课程覆盖广泛、内容前沿

您可以在 EDA Academy(www.eda-academy.com) 学习 PTL、FPGA LUT 设计、逻辑优化实战等全面课程,既有理论延展也有具体案例解析。

II. 学员导师双轨模式

您既可注册成为学员,系统学习,也可申请成为导师,分享您的设计经验与项目心得。

III. 免费订阅 Newsletter

只需填写邮箱,即可持续获得行业最新技术趋势、课程更新与干货分享,无需付费。

IV. 销售联盟计划助力推广与盈利

参与其推广计划,成功推荐课程即享 20%–50% 推荐佣金,让知识传播产生实质回报。

Pass-Transistor Logic 和 FPGA LUT 技术,代表了数字逻辑设计的两种高效方案——一个从晶体管级节省资源,一个在 FPGA 中灵活实现逻辑功能。二者结合,能打造低功耗、高性能的 IC 系统。

借助 EDA Academy,您可以系统深入研习这些前沿内容,成为具备实战能力的设计专家,或通过内容创作与推广,拓展职业与价值空间。欢迎访问www.eda-academy.com,共同探索智慧逻辑设计未来。

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网