日志

什么是Physical only cell?

热度 3| ||

转载自:https://zhuanlan.zhihu.com/p/97912191

平时的设计过程中,新手对于各种的physical only的cell表示非常的不理解,这些又不在网表中,那么他们存在的意义是啥,可以不加么,加的时候又要注意些什么,今天就和大家介绍一下,这些单元他到底有着怎样的作用和要求。

1

Well Tap Cells

一般来说库单元通常会自带well tap,那么n-well就会连接到VDD, substrate就会连接到GND

但是,我们并不需要每个单元都有这样的结构,其实我们对于一个NWELL(也就是说一行)我们仅需要一个连接到VDD,同理substrate也是,如果说我们把这些去掉的话,那么我们就会省下来巨大的面积。所以就会有 “tap-less” libraries,但是由于仅有一个tap会由于NWEL和substrate的阻值而导致latch-up的出现,故而我们会在一定距离内添加well tap单元来避免latch-up效应,

2

Decap cells

decap cell全称Decoupling Capacitor (解耦电容)。在CMOS电路运行过程中,信号的不断变化可能会导致电源电压的不稳定。这可以视为稳定的直流电压(DC)上加了一个交流(AC)干扰电压。如果在电源的Power和Ground之间接入一个适当大小的capacitor,利用capacitor的通交流阻直流的特性,可以平缓电源电压的波动。它自身没有逻辑功能。Decap Cell通常放置在row的两端,或者hard macro的附近。

3

Endcap cells

添加endcap cell主要是为了避免或者是缓和PSE,OSE所造成的影响,意思就是不能让poly和OD周围太空旷,不对称,密度太低。主要是从DFM上考虑的。按理说所有core区域的macro 都要包一圈endcap的,以保护其他周围区域的stdcell的 性能。

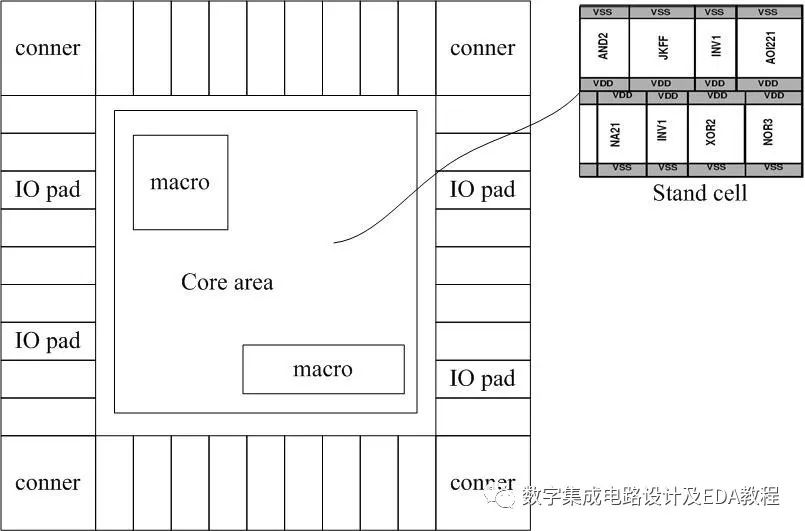

这里也在延伸一下,那就是关于设计中的单元的问题。一般来说,后端place实现的过程其实就是对于网表中的标准单元的进行摆放的一个过程,这里的单元有很多需要我们我们自己去规划,有像时序紧张的触发器需要提前去预摆、一些宏单元需要我们在floorplan阶段去根据飞线去先确定他们的位置等等。后续的话,工具就会根据人为设置的摆放约束,timing-driven si-driven等去进行一个合理的位置摆放。这其中工具也会去对一些单元进行优化,包括像单元的删除和添加的操作。最后才可以得到摆放完成的初步设计。

当然还有些单元也是充当着类似于physical only 单元的左右,他的输入连接到TIEHI TIELOW,不需要的时候仅仅充当一些纯粹的物理单元,只有的用的时候才会成为正式的标准单元,那就是ECO CELLS。

转载自:https://www.eda365.com/thread-365883-1-1.html

1.在设计中添加physicalonly cells

* c4 `! t. z7 |

( O* m- f% t+ E" z! }3 b/ Z

Physical only cells是那些在网表中没有,而在实际芯片中需要存在的一些单元,如电源地IO、给IO供电的IO以及一些衬底、阱接触单元等。7 \5 r6 d% U# M2 \

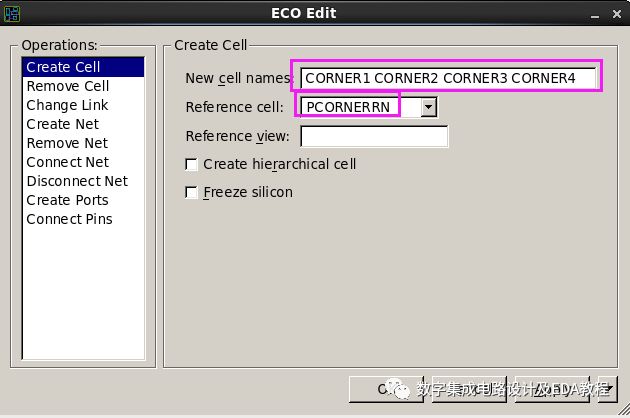

在layout Window的菜单栏中依次选择“ECO”?“CreateCell”。

1)添加IO Corner

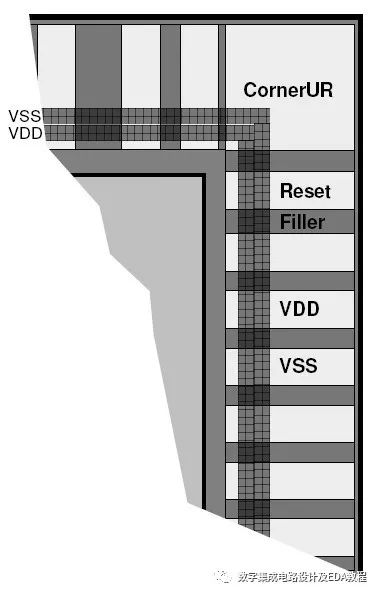

IO Corner的作用是连接芯片拐角处两边的IO Pad,连接衬底以及衬底以上的各个层,使得IO Pad内部的电路形成一个电源地的供电环路。同时也使它们的衬底、阱等各个层连续,不至于出现DRC的违反,如图1所示:

& h1 u0 K0 J# y# o, F3 ^( x6 o

只要在“Reference cell”后边选择相应的参考单元并在“Newcell names”中填写创建的Corner的名字,点击OK即可,如图2所示。

; C% J$ `) H- A/ W' b

2)添加为Core供电的IO(VDD VSS)

3)添加为IO供电的IO(VDD_IO VSS_IO)+ Y, K/ ~/ k9 L4 ?

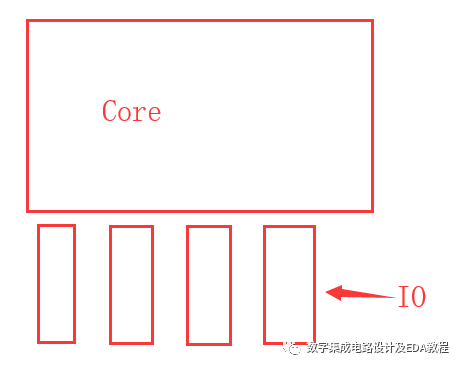

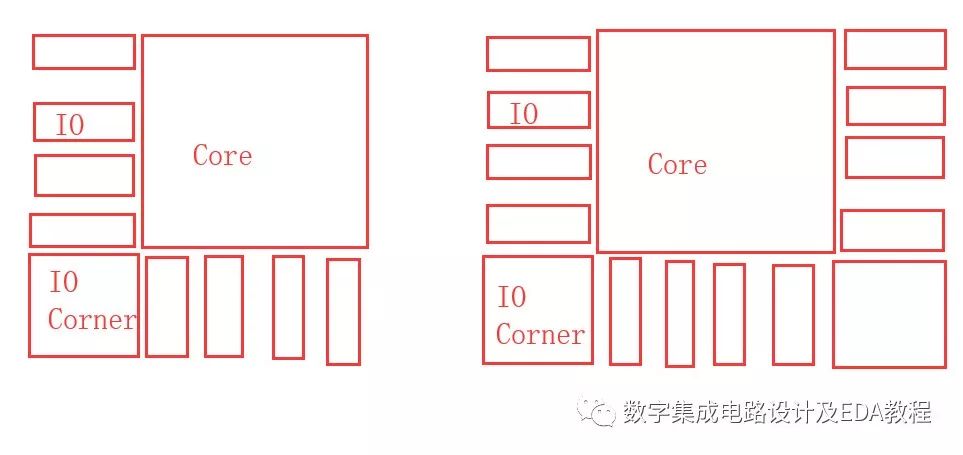

注意,IO Corner是不用围成环的,甚至IO Corner都不是必须的!但是给Core和IO供电的IO是必须的。当芯片只有一边有IO时,或者只有芯片的对边有IO时,此时为了节省芯片面积,不需要IO Corner。如图3所示:

但是对于含IO的边都需要添加一组VDD_IO和VSS_IO来给IO供电。对于右边那种情况,如果用IOCorner将其连接起来的话(面积牺牲比较大,一般也不会这样做),在不考虑IO上的功耗的情况下,只需要一组VDD_IO和VSS_IO就可以了,而非两组。

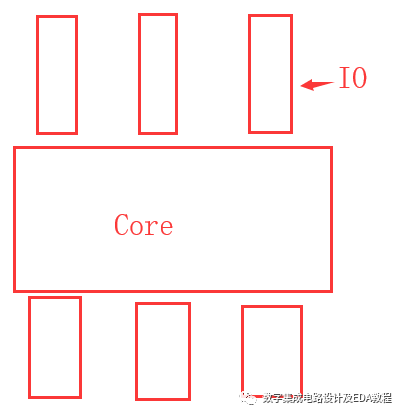

对于相邻两边含IO或者三、四边含IO的情况,一般在拐角处都会加上IO Corner,如图4所示:

4 J: I8 V" t( D) l' m* W

这里以4边都含IO的设计为例进行讲解,因此四个拐角处都需要添加IOCorner,如图5所示:

" P( C/ K3 A! Q

步骤1)2)3)的tcl命令为:

> create_cell {CORNER1 CORNER2CORNER3 CORNER4} {PCORNERRN}% c) r7 ~8 m0 A" g& w4 i" b5 O2 M

> create_cell {VDD} PVDD1RN }% a# h3 D' F

> create_cell {VSS} PVSS1RN; b) i8 H, S c3 g* g5 q

> create_cell {VDD_IO} PVDD2RN

> create_cell {VSS_IO} PVSS2RN

该例子中分别给Core和IO只添加了一组供电的IO,但是在实际项目中,需要考虑Core的功耗以及IR-drop来决定需要几组VDD和VSS以及它们的分布情况。同样需要考虑IO的功耗以及IO上的电压降来决定需要VDD_IO和VSS_IO以及它们的分布情况。6 M8 v0 l+ f0 R

( Z$ r; R6 R2 ]0 x6 e- l6 D

/3

/3

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网