日志

ARC HS3X系列处理器使用总结

热度 1| |

一、概述

前文SOC前端设计总结,模块分类中提到了IP核的二次开发,cpu就是属于需要二次开发的软IP。市面上SOC使用的通用处理器,基本上是以arm、mips、ARC为主。本部分介绍的是Synopsys 的ARC HS36x4 系列处理器的使用总结,该处理器可配置性高,性能强。现在处理器版本已经更新到了ARC HS4X。下面从基本组件、配置、APEX开发、验证、综合、固件开发等方面对ARC HS36x4 系列处理器二次开发所需要做的工作进行一个总结分享,对于不是很熟悉的方面介绍得就更为简略。

二、基本组件

ARC HS36x4 系列处理器包含很多组件(Components),这里只把其中最关键得组件罗列出来,做一些简单介绍,更详细的说明需要参考其DataBook。

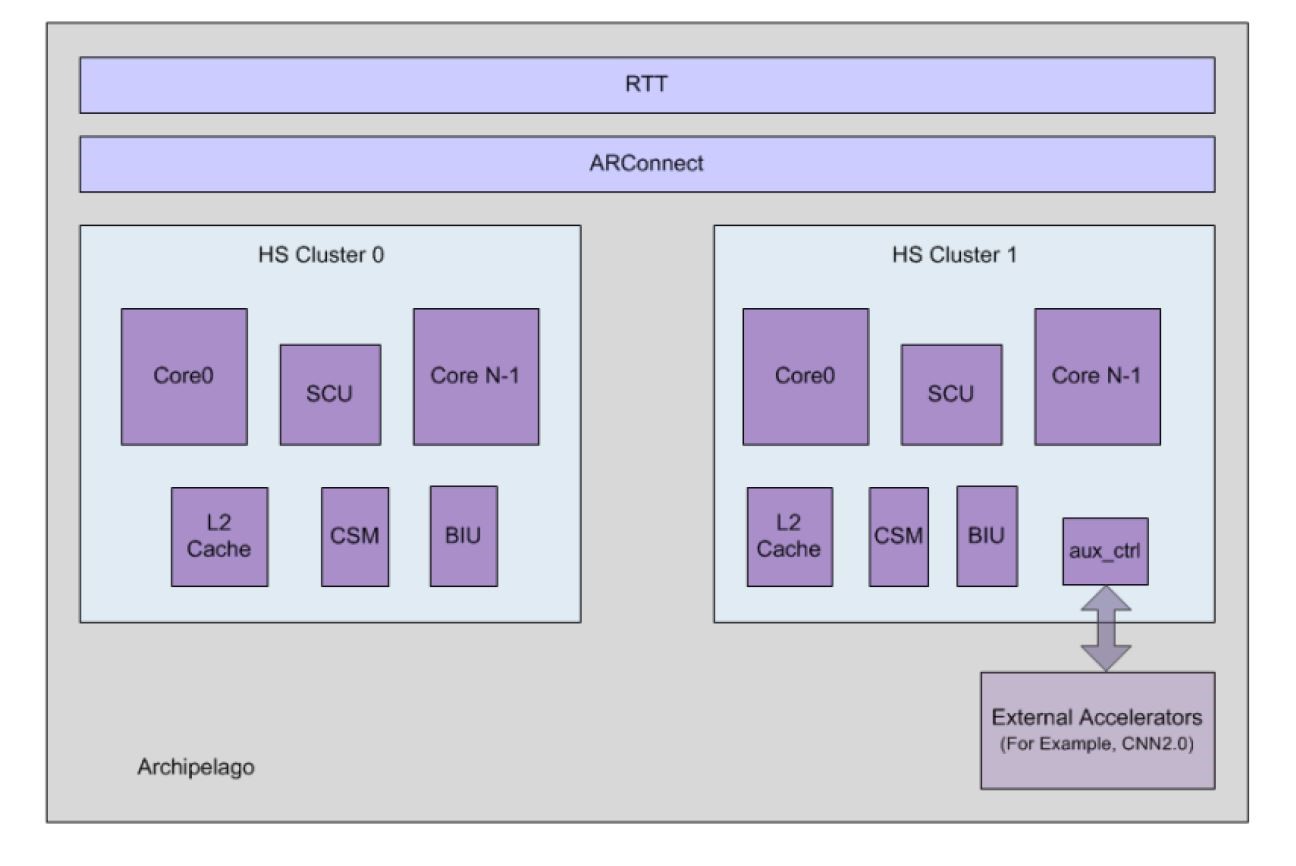

Multi-Core ARC HS Cluster: ARC HS 是一个基于簇的多核处理器。每个簇可以配置成1-4个核。可以有多个簇(cluster)。如下图所示:

Fig 1 ARC HS36

Memory Components:ARC HS拥有region0-region15共16个地址空间,每个region大小为256MB,地址宽度为32bit, region分布如下图所示:

Fig2

这16个region可以分配给如下的memory:

Instruction Closely Coupled Memory (ICCM0, ICCM1)

Data Closely Coupled Memory (DCCM)

Peripheral bus

Cluster Shared Memory (CSM)

External memory bus or busses

Memory Management Unit: memory地址映射单元。

Memory-Protection Options:memory region保护单元,每个region可以设置可读,可写,可执行等属性。

Multi-Core Cache Coherency:多核缓存一致性,是为了在多核CPU运行时,保证缓存的数据正确性的一个组件。

Interrupts:中断控制单元

External Interfaces:外部接口,包括指令总线IBU,数据总线DBU,指令数据组合总线CBU,外围总线LBU,DMI 总线等总线接口。

Cluster Shared Memory:共享memory,在多核CPU里面,保存所有核所共享的一部分数据。

Debug Features: 提供Debug功能,包含JTAG, SmaRT, RTT等模块可以选用。

User Auxiliary-Register Interface:用户定义的辅助寄存器,连接到处理器核,处理器可以直接通过指令来访问这些寄存器的值。

ARConnect:系统组件集合,提供高效的核间通信,中断分发,debug协助等功能。

下面是ARConnect 组件:

■ Inter-Core Interrupt Unit (ICI)

■ Inter-Core Semaphore Unit (ICS)

■ Inter-Core Message Unit (ICM)

■ Inter-Core Debug Unit (ICD)

■ Global Free-Running Counter (GFRC)

■ ARConnect Power Domain Management Unit (ARConnect -PDM)

■ Power Management Unit (PMU)

■ Interrupt Distribution Unit (IDU)

■ ARConnect Slave Interface Unit (ASI)

三、配置

前面简单介绍了ARC HS处理器有哪些组件及其大致功能,本部分讨论ARC HS的配置问题。

处理器核配置:本文中ARC HS处理器是用于SSD控制器中,由于SSD需要做NVMe协议处理、FTL转换、垃圾回收、损耗均衡等工作,任务量很大,所以处理器核心就按照最大的来配置,为4核。每个核负责不同的任务。其它情况可按照需求配置。

Memory配置:根据需求配置ICCM, DCCM ICAHCE DECHAE

中断配置:根据需求配置中断的数量,中断的方式-沿触发或者电平触发。

总线配置:根据需求配置IBU,DBU,CBU,LBU等各类总线接口,可以配置为AXI, AHB,BVCI等总线接口。

ARConnect配置:根据需求配置ARConnect的组件。

Debug配置:根据需求配置JTAG, RTT。

配置ARC HS处理器,使用的软件是synopsys公司的ARChitect。ARC HS配置选项非常多,这里只是简单罗列了最主要的可配置组件。至于软件的使用,这里就不做介绍了。具体配置按照实际需求进行,可能会反复修改。配置这边倒是没有太复杂的地方,复杂的地方在后面。

四、APEX开发

前面的各类配置均可以在ARChitect软件下通过选择各种选项即可配置完成。但APEX要在ARChitect软件下配置一些选项,但远远没有这么简单。APEX 全称为the ARC Processor Extensions,是对ARC 处理器的一种扩展,具体说来就是ARC 处理器可以自定义指令,可以选择使用core register, auxiliary register。这对于SSD的开发而言是极为重要的一点,它可以简化某些操作,通过自定义指令的方式,让CPU来处理一些复杂操作,简化模块设计。

4.1 指令相关

指令一共有三种类型type0,type1,type2,每一种类型支持不同的功能,其中type2支持64位的操作数。指令执行的周期可以是固定的,也可以是自定时的,指令执行过程可以是阻塞的,也可以是非阻塞的。以上是常用的指令相关的参数,其余参数根据需要再添加。

4.2 设计流程

根据实际需要a) 确定是否使用core register, auxiliary register, 2)确定指令个数,指令类型、操作数宽度、操作数个数、指令周期、阻塞与否。在准备工作完成之后即可将这些参数填入ARChitect软件的对话框中。接下来的RTL设计与普通RTL设计相同,需要注意的一点是,如果没有其他需要添加额外的input, output,那么RTL代码的input , output是固定由软件自动生成的,如果有额外的input,output信号,则需要手动添加进去。所以,在设计RTL的时候需要特别关注这些自动生成的interface的时序,时序如果不能匹配好,那么自然不能达到想要的功能。

4.3 验证流程

编写完RTL代码之后,下一步就要写验证代码了。因为APEX是我们自定义的指令,所以验证指令的方式就是通过写C code的方式来验证。写完C code之后,点击build按钮,等一会儿ARC HS CPU就build完了,然后就可以开始进行验证。Synopsys 已经提供了MetaWare Debugger工具方便我们进行APEX扩展指令的验证。步骤:a)编写C code, b)编译C code, c) 在指定路径下运行mdb -rascal tests/extension/your_apex 即可调用MetaWare Debugger工具来验证,仿真过程中可以通过DVE波形查看工具来看波形。

利用MetaWare Debugger工具来验证APEX有许多不足之处,首先验证代码是C code,所以有时候想要生成随机的输入激励会比较困难,ARC HS自带的C编译环境不带有随机函数。此外,利用MetaWare Debugger工具来验证APEX,仿真时间会特别的慢,尤其是加入打印函数之后。所以,初步简单的功能验证可以交给MetaWare Debugger工具来验证,但更进一步的进行随机激励验证,仍然需要使用传统的UVM验证环境来验证,这样验证的灵活性会更高,验证得也更为全面。

五、综合

Synopsys为ARC HS CPU的开发提供了一份综合流程。在build完CPU之后,会生成相关的综合setup文件,SDC约束文件。但是,还需要做一些手工替换的操作才能进行DC综合。

流程:1,在综合setup文件中,设置工艺库相关文件及路径;2,修改/删除SDC文件中不符合当前综合的约束条件;3,替换syn_cell同步单元逻辑,替换clock_gated门控单元逻辑;4,替换memory,build完之后的CPU,如果不是严格按照Synopsys要求的准备好相关的软件和工艺库,那么生成的CPU的memory是一个二维数组,是不符合综合要求的。必须予以替换。当以上步骤做完之后,即可进行综合操作,使用提供的make指令即可。

这样依赖Synopsys提供的半成品setup文件,SDC约束文件来进行综合的过程是有不足的。不能够满足实际的需要,因此,这样的综合结果只能作为一个参考,真正的综合还是要依靠前文提到的利用makefile做出来的统一综合流程。只有这样才能将项目管理统一起来。

六、固件开发

涉及到了CPU的二次开发,那么CPU固件是绕不开的。针对不同应用场景的CPU需要开发不同的固件。SSD的固件主要集中在处理NVMe协议,FTL转换,垃圾回收,损耗均衡等功能上,所知甚少,这里不再多说。

七、ARC RTT

RTT 全称Real Time Trace, 属于ARC HS系列的debug模块之一。说到RTT是如何工作的,必然要谈到我们是如何Debug CPU的。Debug CPU, 主要在于追踪CPU执行程序过程中是否读取或写入了某个地址,某些地址,是否读取或写入了某个数据。这是Debug的核心所在。所以RTT的功能也就相应的更为明了——DEBUG 特定的地址、特定的地址范围、特定的数据。

RTT的使用:1,设置想要Debug的源—PC,core register, auxiliary register, memory;2,设置触发的类型,单个地址触发,范围地址触发,数据触发,3,设置想要触发的地址,地址范围,数据值。4,设置触发之后,产生的message存放在memory的某地址范围内中还是直接通过端口直接输出到CPU外面。5,解析message,看是否想要的Debug的源已经被触发。

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网