日志

Vivado中将verilog代码封装成IP(转)

| ||

Xilinx的Vivado采用原理图的设计方式,比较直观适合大型项目,我们自己的code都需要封装成user IP。

这里主要介绍怎么把多个关联管脚合并成类似bus的大端口

第一大部分 选择source文件

先新建一个project,把要package的v文件加进去,一般都会先做功能仿真

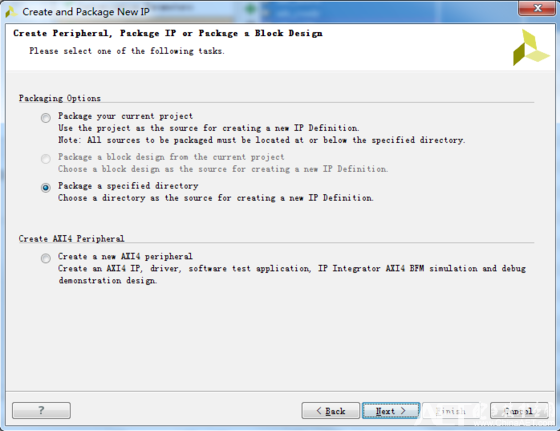

Tools->Create and Package IP,我个人喜欢用第一项current project;

第二项block design用来封装多层嵌套的大IP;

第三项是封装指定文件夹下的source文件,也非常好用;

第四项是新建一个AXI4接口的IP,比如说我要自己写AXI-HP的接口就用这个;

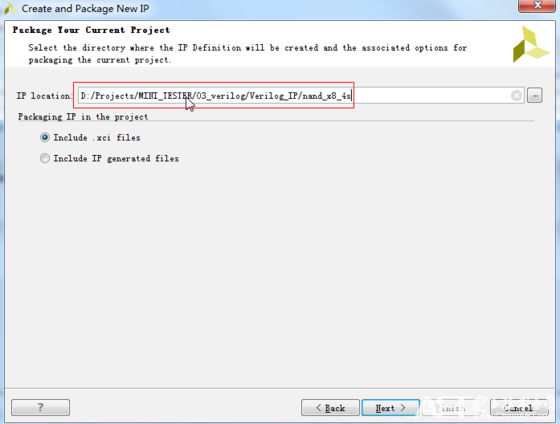

建个文件夹verilog_IP,存自己的IP,每个IP再建个子文件夹

第二大部分 端口分组合并

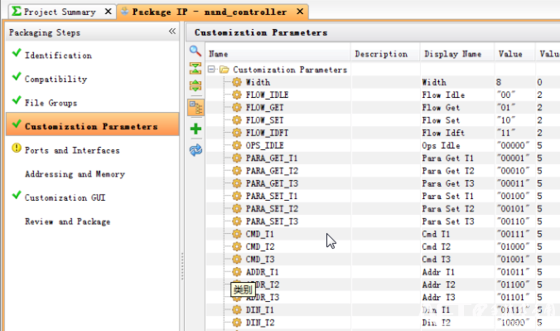

Parameter页除了第一个Width是传递参数,其他都是状态机的参数,可以全部删掉

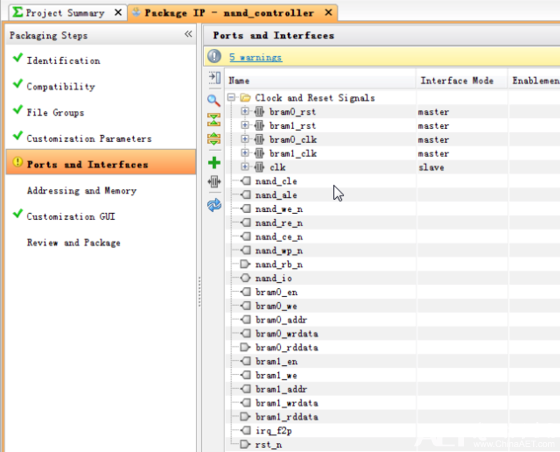

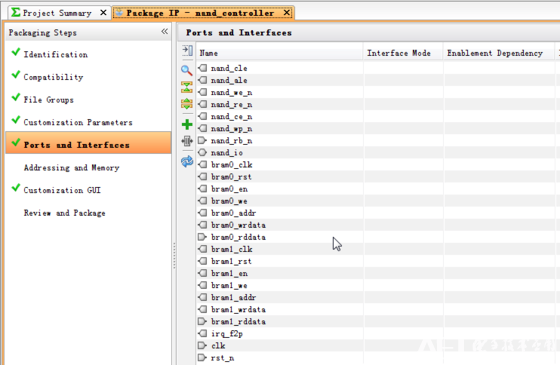

Ports页会自动把能识别的clk和rst都分类好,但不是我们想要的分类,要删

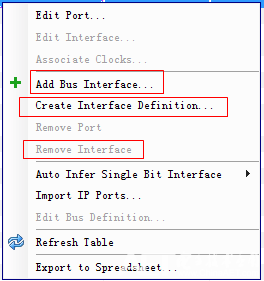

选中右键 Remove Interface

接下来就是信号分组,也叫bus interface

分两种情况,需要跟xilinx的IP对接的标准接口要用Add Bus Interface,我们自己定义的接口用Create Interface Definition来新建;

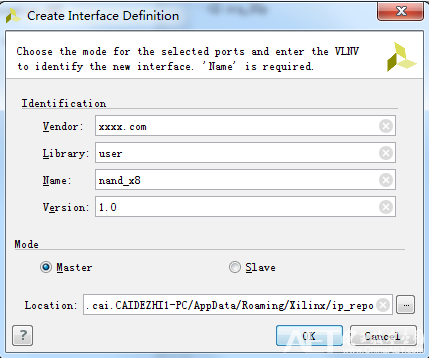

前面的port是打算引出芯片的nand接口,选中右键Create Interface Definition,名称nand_x8

后面的bram0和bram1都是要跟标准AXI_BRAM接口对接的,各自选中右键Add Bus Interface

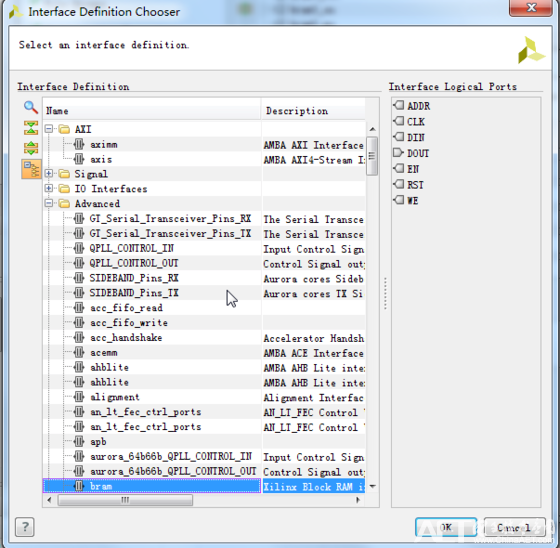

先是标准接口,默认是aximm_rtl,要换成bram

打开浏览进入Chooser页,选Advanced页的bram接口

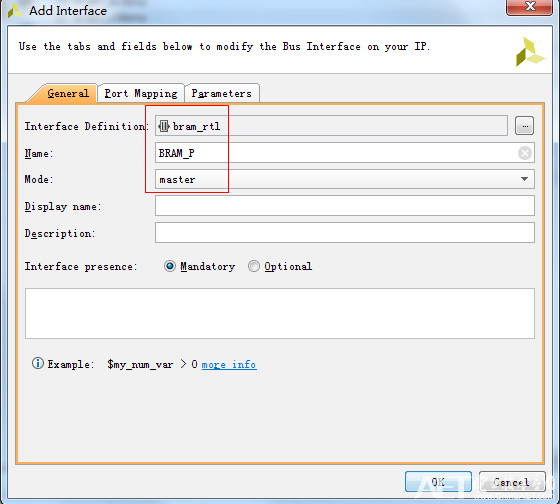

选好后如下,General页,这里Mode选master,跟你代码的in/out有关

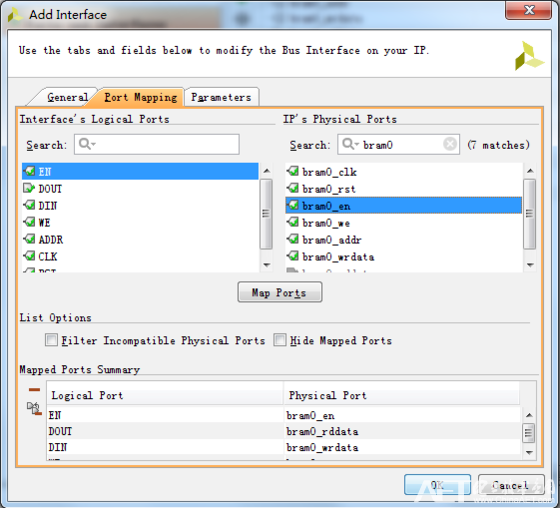

然后Port Mapping页,逐个接口map,主要依据in/out/inout类型关联。接口太多先search筛选

接着是user定义的接口

如果你有多个相同的bus接口,可以每个都新create,也可以先create一个,然后后面几个用Add Bus Interface的方式。

在Chooser中的User子项找到nand_x8接口,然后逐个map。建议用后面一种,因为在你把IP引出port的时候命名会保持原值,否则你还得逐个改信号名。

补充:请把Location的位置改成自己IP下的文件夹,放在Roaming系统文件夹下下次就找不到了。

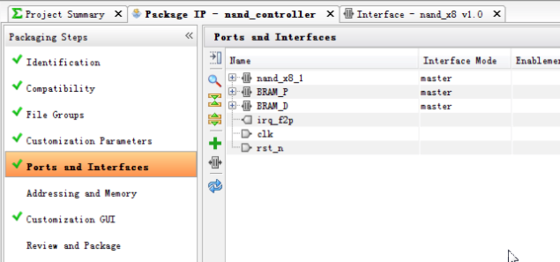

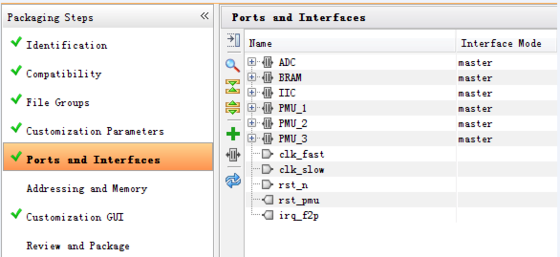

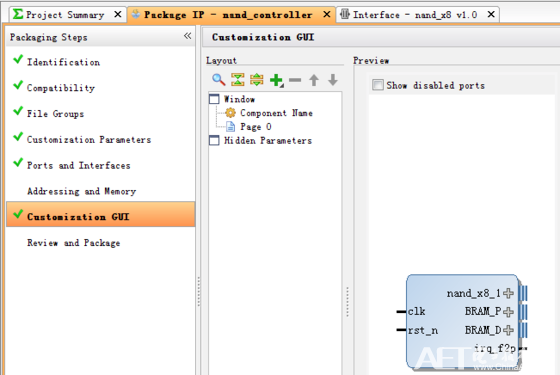

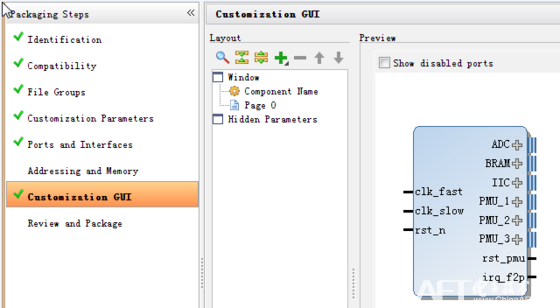

最终的界面就清爽了,折叠成了3个bus接口,可以再右键Edit

参考二

最终框图。输入脚在左,输出脚在右

参考二

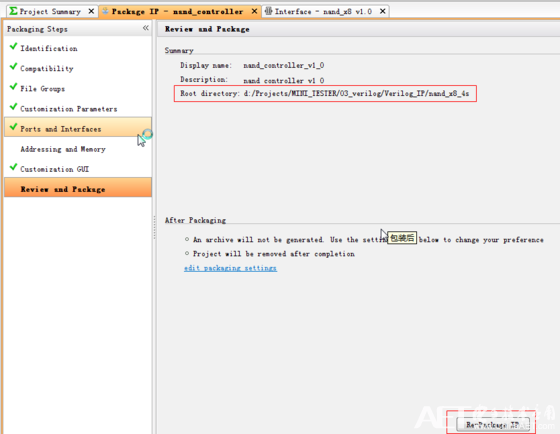

确认下名字和路径,全部OK后点Packaged IP就完成了

第三大部分 调用 IP

然后你在IP Catalog中是可以选中新IP的

如果后续再建project时,搜不到自己的IP,请按照下面的方式添加IP路径

IP的更新也有很多注意事项,在下一篇中详细说明。

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网