1、set_false_path

日志

异步时钟约束

热度 16| |||

对于异步时钟有四种方法进行约束。本文介绍了每种方法的优缺点:

这是最原始的方法,在时序分析设计早期比较流行。

这种方法有两个缺点:

a. 两个方向都需要约束:clock1->clock2 以及 clock2->clock1

b. 该路径没有时序要求,因此理论上路径延迟完全依赖于所使用的工具。而且这两种路径可能导向不同的节点,因为我们没有办法规范它们来满足任何具体的要求。

2、set_clock_groups

该方法已被引入 SDC 中,与方法 1 相比有以下三个主要优点:

a. 只需要指定源时钟与目的时钟,尽量减少 XDC/SDC 文件的长度

b. 与 set_false_path 方法相同,这里的路径也没有时序要求。但是它考虑到了信号完整性方面的问题,而 set_false_path 方法并没有

c. 在基于 FPGA 设计领域,可以说这是不重要的,因为在设计 FPGA 器件时信号完整性方面已经被考虑到了

d. 这种方法带点哲学思辩的方法论

e. 当我们使用 set_false_path 方法时,只是指定了这条路径不需要约束的,但是并没有明确的解释路径不需要约束的原因

f. 拿异步时钟来举例,在实际情况下,路径并不是错误,所以时钟信号会通过这条路径,set_false_path 则可作为一种机制来告知工具,时钟信号不约束走这条路径。

在 set_clock_groups 这种方法中,我们指定了准确的原因,即为什么每个时钟信号组是不同的。实际上它们不能进行时序约束的原因完全是由你的意图决定的。因此这也可以作为一个注意事项,可以更加容易理解具体约束设计的原因。

通常情况下方法 2 要优于方法 1,主要是因为以上的 b 和 c 因素,其次 a 因素也是比较重要的。

3、set_multicycle_path

大约在21世纪中期的时候,设计者开始从 set_false_path 方法转向 set_multicycle_path 方法。方法 1 和方法 2 并没有约束一个路径 —— 每条路径的延迟是任意的。这种方法提供了跨越某个节点的路径的延迟上限规定。

4、set_max_delay

这种方法的效果与方法 3 相同。同时与 set_multicycle_path 方法相比,set_max_delay 方法更能表现出设计者的意图。

如果你想选一种方法,我建议的顺序是:4>2>3>1,有时我更倾向于选择方法 2。

==========================================================================

具体通过set_max_delay 约束

DC综合约束012_异步fifo中的格雷码设置max_delay

1、异步fifo中格雷码约束

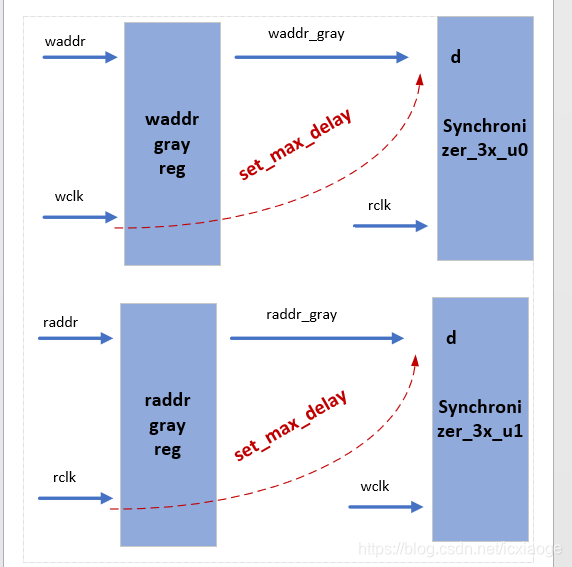

为了保证异步fifo的功能和性能保证,需要在综合约束文件sdc中,约束异步FIFO格雷码的最大延时。约束如图所示:从格雷码寄存器的时钟端口---->到3级同步器的输入端口的最大延时。写地址waddr和读地址raddr格雷码同步都需要设置set_max_delay。此处set_max_delay是为了保证源端信号到达目的端被采样时的格雷码唯一bit跳变特性。延时可设置为读写时钟中最快时钟周期的一半,也可以设置成源端时钟的一半,或者设置成源端时钟的倍数且bit间的skew明显小于一个源端时钟周期。

set_max_delay [expr 0.5*$period_fast_clk] -from [get_pins “详细路径1/waddr_gray_reg_*_/clocked_on”] -to [get_pins “详细路径1”/synchronizer_3x_u0/同步器件名称/d”]

set_max_delay [expr 0.5*$period_fast_clk] -from [get_pins “详细路径2/raddr_gray_reg_*_/clocked_on”] -to [get_pins “详细路径2”/synchronizer_3x_u1/同步器件名称/d”]

NOTE:路径填写的是模块例化名称,同步器_u*不能丢。

2、为什么要设置读写地址格雷码的max_delay?

如果不设置读写地址格雷码约束:会出现以下两种情况:

格雷码各bit位延时不一致---导致同步器采样的地址不符合gray规律,afifo功能异常。

格雷码到同步器的延时有好多个周期----异步afifo性能下降

情况1:格雷码各bit位延时不一致

格雷码各bit位延时不一致,导致afifo功能异常

假设3bit的gray码各比特位延时不一致,比如gray[1]延时比gray[0]多一个采样周期,比如gray[2]延时比gray[1]多一个采样周期,如图所示同步器syn_3x采样端的数据入口处的波形。

虽然源端格雷码是符合要求的,但是由于格雷码延时不一致,导致采样端采样的格雷码不符合要求。

情况2:格雷码到同步器的延时有好多个周期

格雷码到同步器的延时越长,流水间隔越大,afifo性能越差。

假如afifo深度为16,写地址waddr_gray码到同步器的延时为8个周期,加上同步器3个周期,写数据侧写入数据后,至少需要11个read_clk后读数据侧empty信号无效,也就是说至少11个read_clk后读侧才能读数据。而如果写地址waddr_gray码到同步器的延时为1个周期,则写数据侧写入数据后,只需要4个周期,读侧就能读数据了。

————————————————

版权声明:本文为CSDN博主「IC小鸽」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/icxiaoge/article/details/88925743

全部作者的其他最新日志

- • 2024-12-17

- • DFT

- • 2024-11-18

- • IO pad

- • Xilinx-7系列FPGA

发表评论 评论 (3 个评论)

- 回复 shidihahaha

- wclk reg/ck --> rclk reg/D max delay设置成快时钟周期的一半。意思是这条异步路径的约束反而要比同步的严?

- 回复 songdengsheng

- 让我回忆起max delay了。false path只有静态类似的才搞. muticycle和group都是用过给同步

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网