来源:EETOP编译自tomshardware

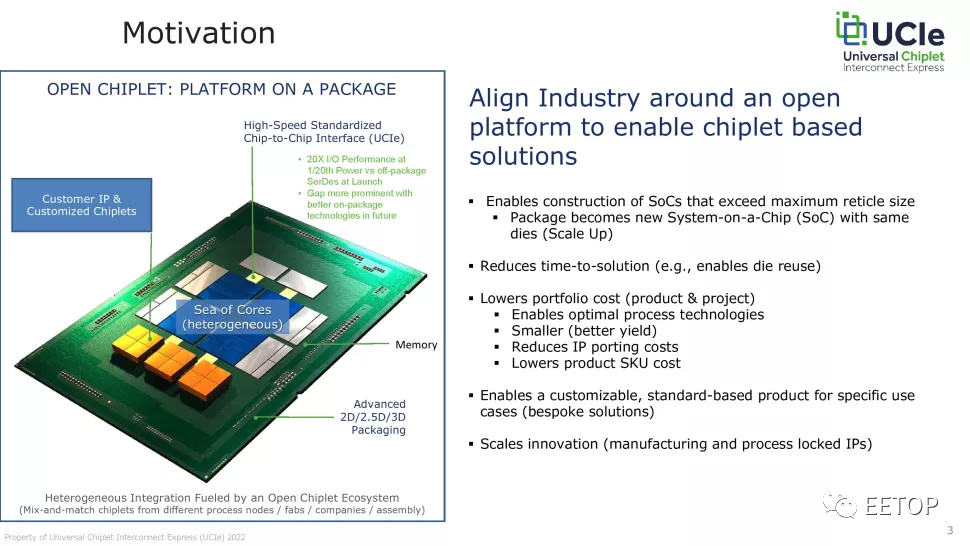

英特尔、AMD、Arm、台积电和三星等众多行业巨头今天宣告成立了新的通用小芯片高速互连 (UCIe) 联盟。目的是通过开源设计实现芯片之间的芯片互连标准化,从而降低成本,促进更广泛的验证芯片的生态系统。最终,UCIe标准的目标是像其他连接标准(如USB、PCIe和NVMe)一样普遍和通用,同时为小芯片连接提供卓越的功率和性能指标。值得注意的是,所有三个领先的代工厂都将采用这项技术,还有x86和Arm生态系统(不过奇怪的是RISC-V和Nvidia没有参加)。

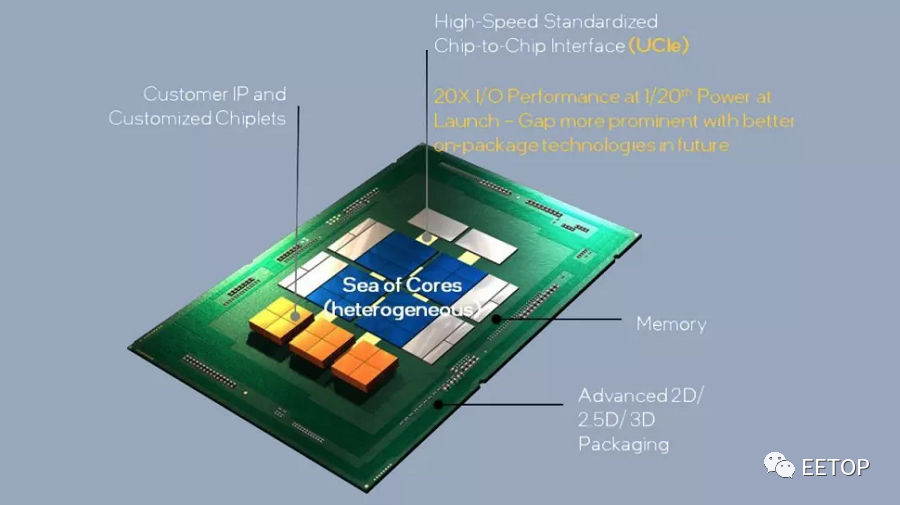

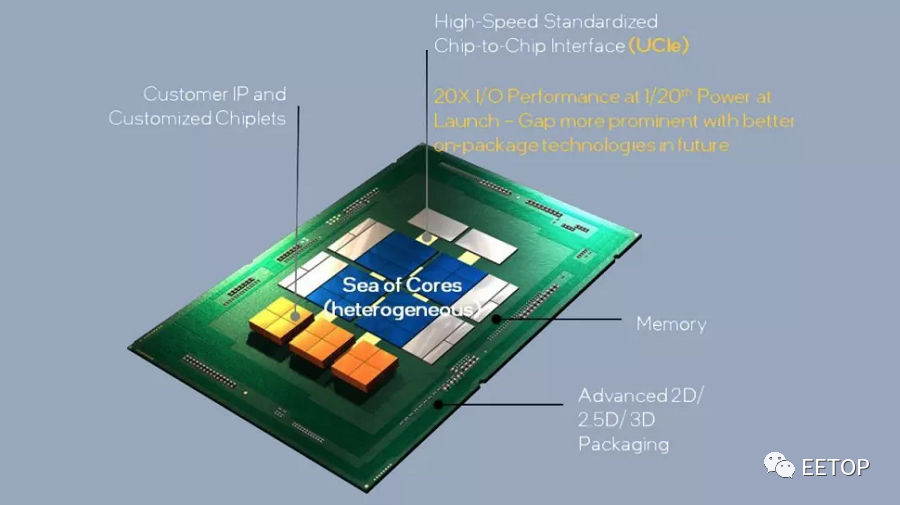

小芯片的好处,如降低成本和在单一封装中使用不同类型的工艺节点,是众所周知的,也是芯片制造商在摩尔定律逐渐失效的情况下努力解决日益困难的扩展问题的关键。芯片的长期愿景一直是让芯片制造商能够开发他们自己类型的专用芯片,然后将它们与其他公司现成的芯片设计配对,从而使他们能够以搭乐高的方式构建自己的芯片,在降低成本的同时缩短上市时间。然而,小芯片之间缺乏标准化的连接导致了各种定制的专有互连,因此现代小芯片当然不能与其他设计即插即用。此外,该行业长期以来一直深受小芯片设计和互连缺乏标准化验证和验证的困扰,这使得现成的小芯片生态系统变得无法实现。这种新的UCIe互连将实现小芯片之间的标准化连接,如内核、内存和I/O,其外观和操作类似于片上连接,同时也可以实现与其他组件的片外连接--这些设计甚至可以为机架级设计实现足够低的延迟和足够高的带宽--并且依赖于现有的协议,如PCIe和CXL。

图5

图6

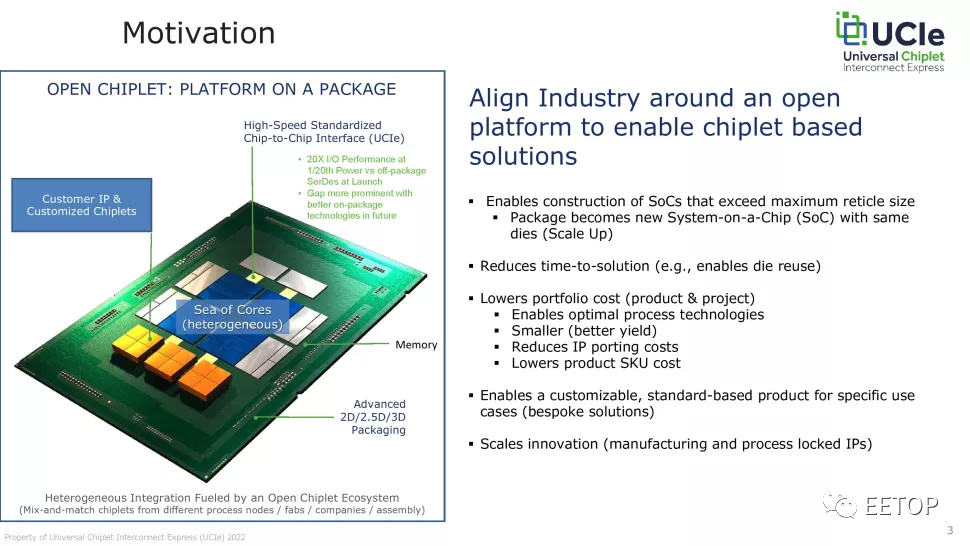

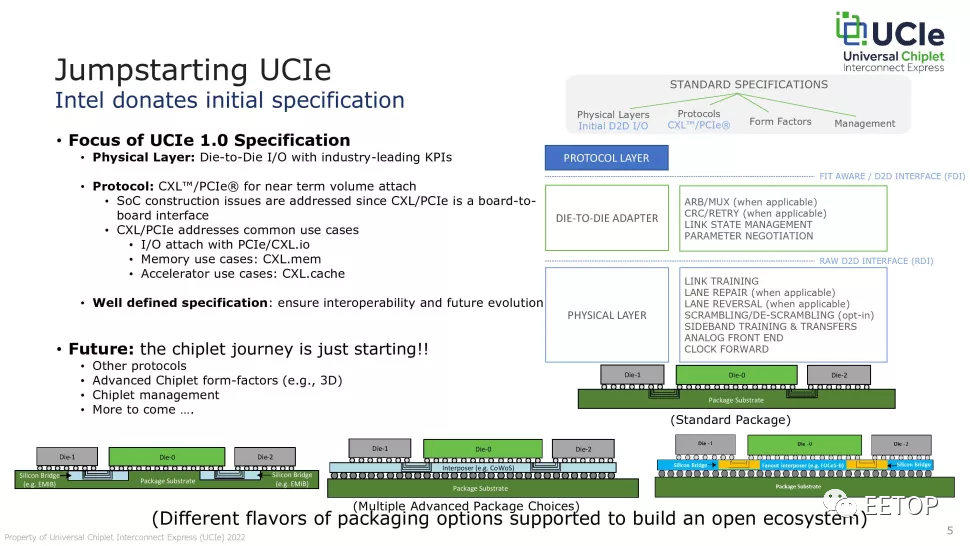

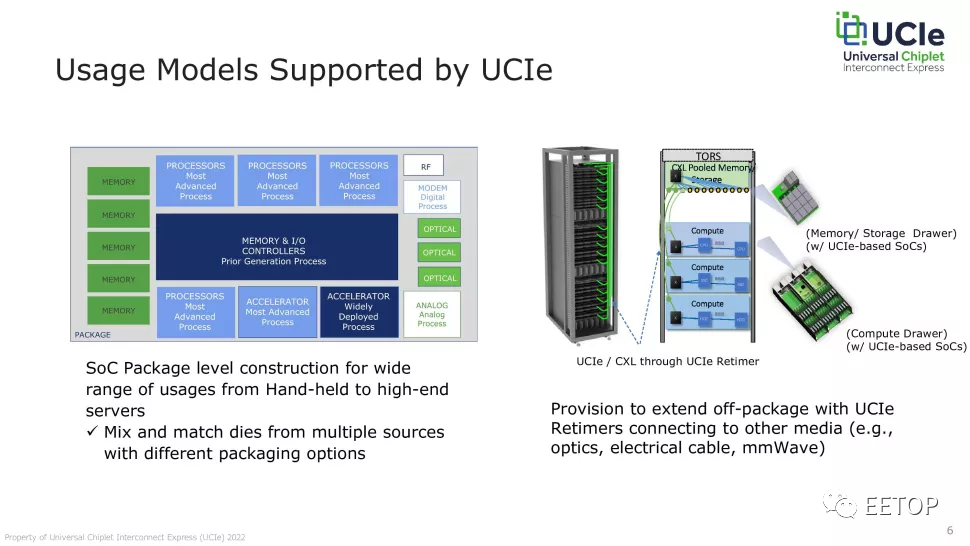

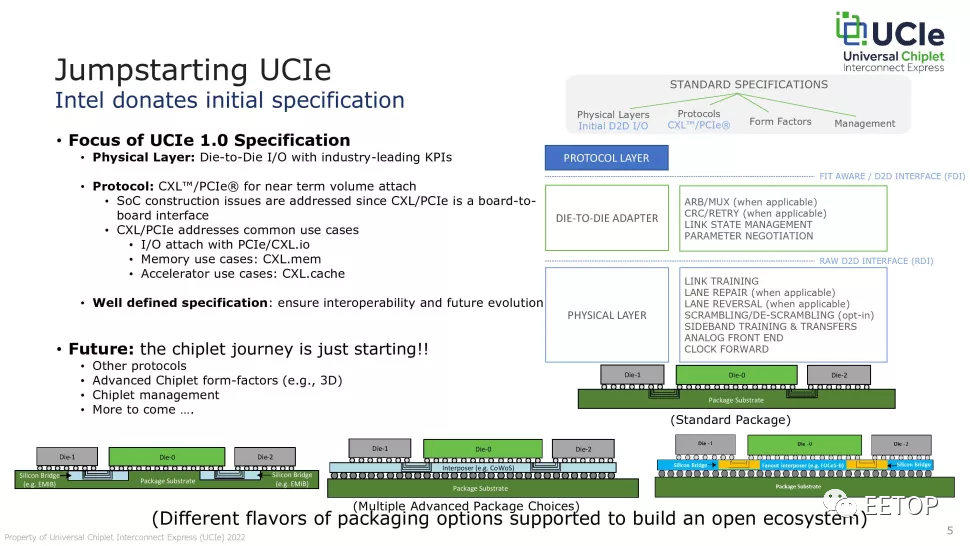

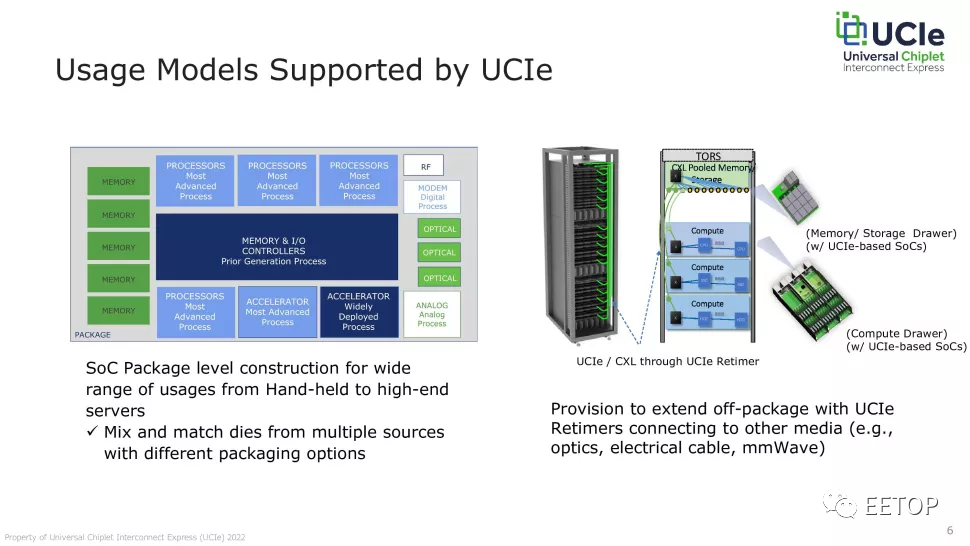

图7

UCIe 是一种分层协议,具有物理层和 die-to-die 适配器。正如您在第二图片中看到的,物理层可以包含来自多家公司的所有类型的当前封装选项。这包括标准 2D 封装和更先进的 2.5D 封装,如英特尔的EMIB、台积电基于中介层的CoWoS,以及扇出中介层方法,如 FOCoS-B。UCIe 标准未来也将最终扩展到 3D 封装互连。协议层在物理层之上运行,最初的规范依赖于PCIe或开放的Compute eXpress Link(CXL - 最初由英特尔捐赠)协议。PCIe协议提供了广泛的互操作性和灵活性,而CXL可用于更先进的低延迟/高吞吐量连接,如内存(cxl.mem)、I/O(cxl.io),以及加速器,如GPU和ASIC(cxl.cache)。虽然该规范以PCIe和CXL作为当前的协议开始,但它将在未来扩展到包括其他协议。英特尔之前为EMIB使用了两种协议;高级互连总线(AIB)和UIB。英特尔将AIB作为一个开源的免版税标准捐献出来,以促进标准化的芯片生态系统,但这并没有获得很多行业的支持。相比之下,CXL现在是一个被广泛采用的标准,因此与UCIe一起使用它更有意义。然而,UCIe和AIB在本质上并不兼容(特殊的子集设计可以实现两者的使用),因此虽然英特尔将继续全面支持当前的AIB实现,但它将停止所有进一步的开发并迁移到UCIe。UCIe 规范还包括一个重定时器设计,可以扩展芯片封装外的连接,实现与其他组件的光学和电气连接,例如内存池、计算和加速器资源。鉴于出色的性能指标(我们将在下面介绍),UCIe 联盟设想互连最终使该行业几十年来一直在努力构建有意义的数量的机架级分解系统类型成为可能。芯片到机架的连接可以使用原生 CXL 进行 PCIe 通信(无需转换),或许最终提供此类设计所需的延迟和带宽。此外,如果需要,可以使用其他类型的协议。

图8

图9

图10

图11

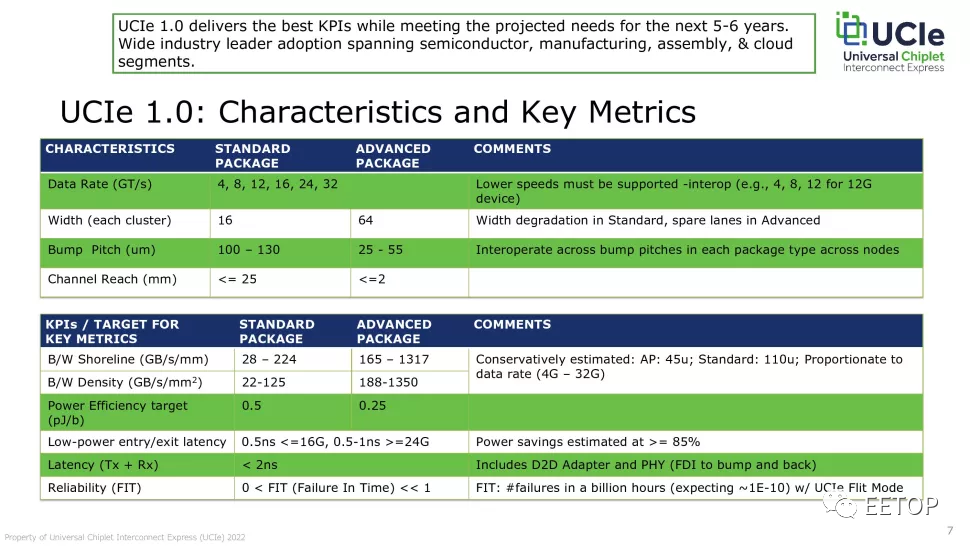

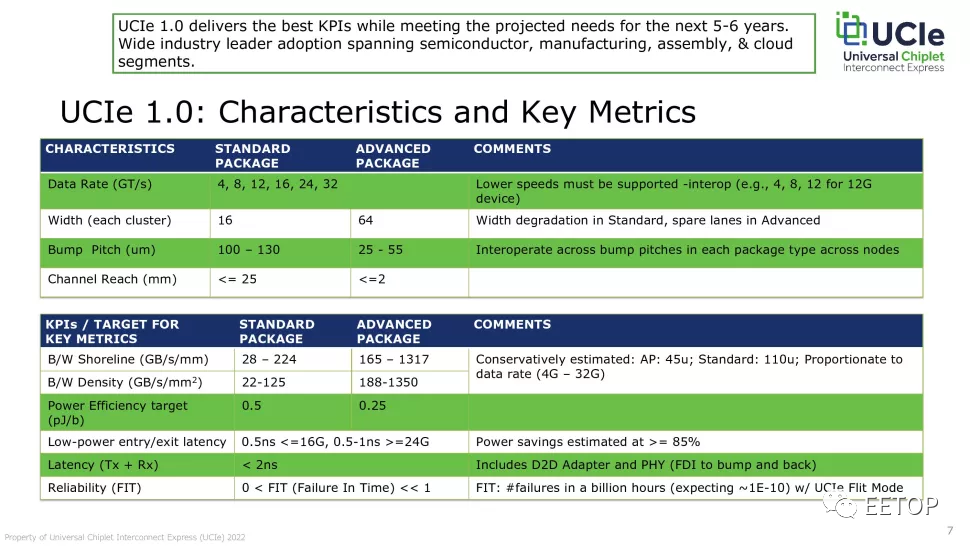

该联盟已经概述了非常激进的性能和面积目标,并且有许多活动部件可以为广泛的用途定制连接 - 不仅仅是最高端的设备。该联盟将目标划分为两个广泛的范围,使用标准的 2D 封装技术和更先进的 2.5D 技术(EMIB、CoWoS 等)。自然,先进的封装选项提供更高的带宽和密度。可配置因素包括数据速率(跨越 4 到 32 GT/s)、宽度(通道数)、凸块间距(连接密度)和通道范围(物理连接的长度)、延迟在 2 纳秒以下。值得注意的是,通道范围从 2 毫米延伸到 25 毫米,可实现非常紧密的芯片对齐,以实现更长距离的应用。但是,与第一张图片中概述的其他指标一样,这些只是主要目标。例如,设计人员可以简单地降低频率以将连接延伸到 25 毫米以上。对于性能最高的设备,通常都是将尽可能多的低延迟带宽塞进尽可能小的区域。然而,大多数设计并不要求这种级别的性能,所以设计师可以使用多种手段来定制自己的设计。因此,第一张图片中的“target for key metrics”将根据不同的设计选择而变化。例如,BW Shoreline (GB/s per MM) 和 BW 密度 (GBs permm^2) 预测基于 45 微米凸块间距。但是,该规范支持低至 25 微米的凸块间距,这将使这些值增加三倍或更多。这意味着对于 UCIe 连接,我们可以看到每 mm^2 的吞吐量高达 3.8 TB/s。但是,放宽这些值可以提高电源效率,突出显示可用于满足几乎任何用例的多个优化轴。此外,该联盟在构建规范时考虑了电源效率,适应了诸如从开机和关机状态快速进入/退出(亚纳秒级)等高级功能。总体而言,UCIe 规范旨在使封装互连看起来尽可能类似于片上互连,同时提供大量选项,可以实现所需的任何类型的性能或封装技术。然而,UCIe规范确实有一个竞争对手,即开放计算项目的Bunch of Wires(BoW)规范。BoW规格的设计也是为了使芯片设计大众化,并拥有令人印象深刻的性能规格,但它并不那么灵活。例如,BoW提供0.7至0.5 pJ/bit(每比特皮焦耳)的功率效率,而UCIe可实现0.5至0.25pJ/bit。(这可能因使用的工艺节点而不同)。 BoW 规范支持固定的 16 GT/s,而 UCIe 是可配置的,最高可扩展到 32 GT/s。UCIe 在其他指标方面也处于领先地位,例如Shoreline带宽密度(1280 Gbps 对比高达 3.8 Tb/s),并且还仅限于 MCP 封装,而 UCIe 可以支持大多数 2D 和 2.5D 封装选项。 图12

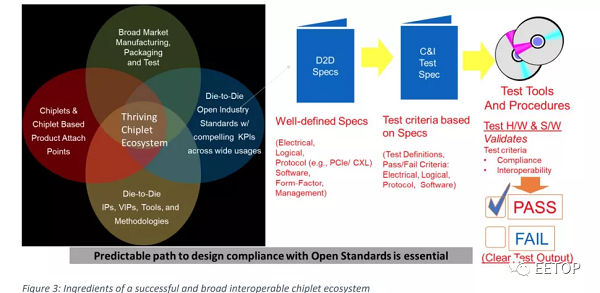

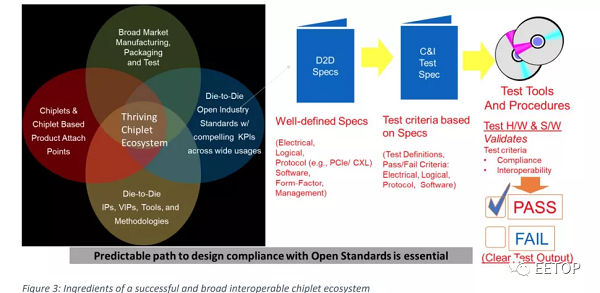

标准化互连是提高任何设备更广泛的验证、合规性和互操作性的第一步。不幸的是,半导体行业长期以来一直缺乏被广泛接受的小芯片验证、验证和资格认证流程,从而阻碍了更广泛的采用。UCIe 联盟非常关注这些方面,在最初的 UCIe 1.0 规范中有一章专门针对验证和内置功能(如专用边带通道)来帮助完成这些工作。

总体而言,UCIe 规范看起来很有希望,但广泛的支持至关重要。正如我们在 CXL 规范中看到的那样,该规范现在在行业中占有一席之地(将得到英特尔 Sapphire Rapids、AMD 的 EPYC Genoa 和 Arm 设计的支持),该联盟带着一份蓝筹赞助商名单进入市场,我们预计此列表的增长速度与 CXL 一样快。赞助商包括 AMD、英特尔、三星、Arm、日月光、台积电、谷歌、Meta、微软和高通。这是一份令人印象深刻的名单,其中包括前三名的代工厂,这很重要。值得注意的是,Nvidia 目前没有参与,我们也没有看到 RISC-V 的迹象。 UCIe网站已上线(https://www.uciexpress.org/),最新的UCIe 1.0 规范已发布。

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网