日志

【转载】AMS仿真详解

热度 13| ||

使用Cadence AMS仿真器做數模混合仿真

https://blog.csdn.net/mymatin1004/article/details/98804521

二、Cadence 基于ams仿真器的混合信号电路仿真

P.S.:这里假设大家曾经有一些在 Cadence 中 Analog 电路的操作经验如: check and save : Shift + x

2.1、建立数字(Digital)模块

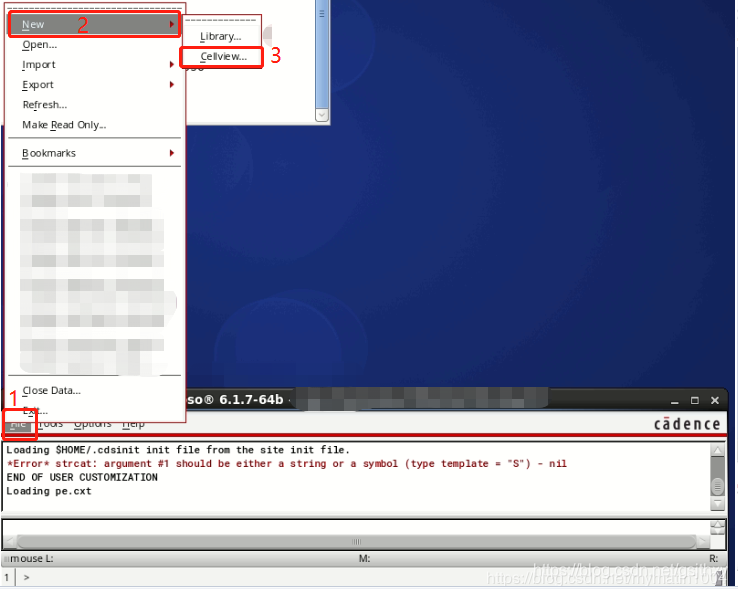

首先,打开软件,点击 File -> New -> Cellview 准备为我们的将由 ** verilog** 写成的半加器新建一个 Cellview

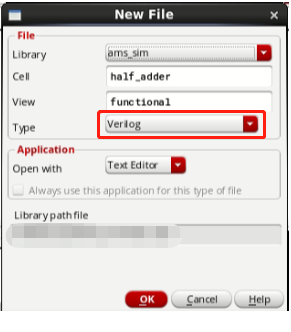

之后会弹出新建文件的对话框,这里由于我们将使用 ** Verilog** , 因此在填好 ** Cell ** 的名字之后,记得在 ** Type** 中选择 ** Verilog**, 相应的, View 也会变成 functional 。然后点击 OK 。

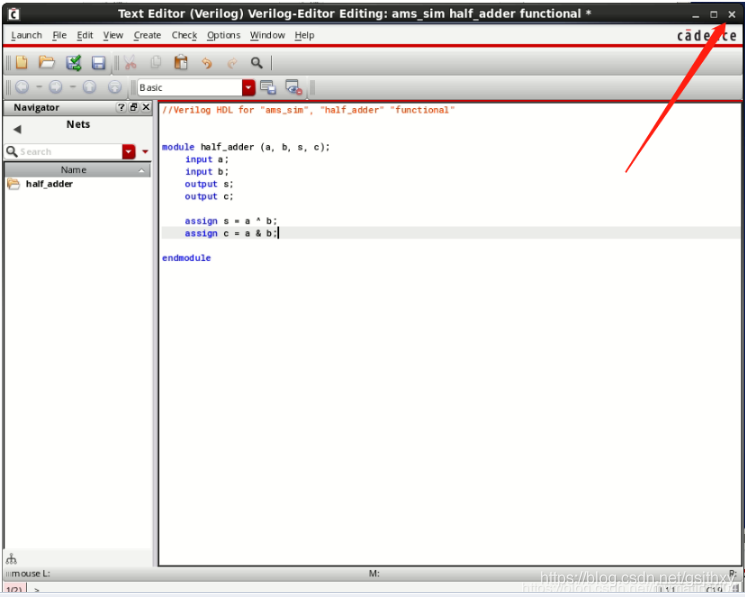

接下来会弹出下面这个界面(和普通编辑器蛮像),在里面写好 Verilog 之后,先点击保存,然后点击右上角的 ** X** 来关闭窗口。

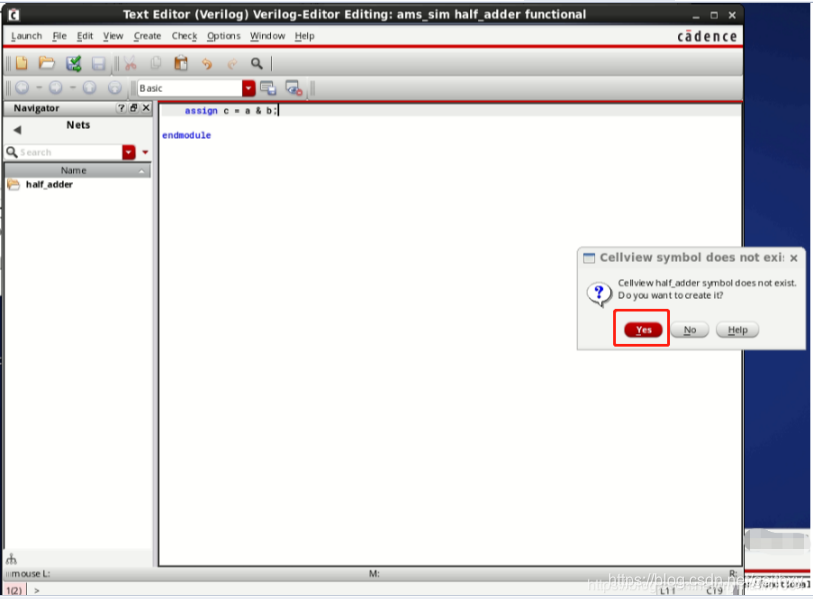

这下就会出现一个弹窗,告诉你这个模块还没有 symbol 问你要不要新建一个。这个时候当然要点击 Yes。

然后可能就看起来没有什么事情发生了(其实对应的 symbol 已经建立好了)。

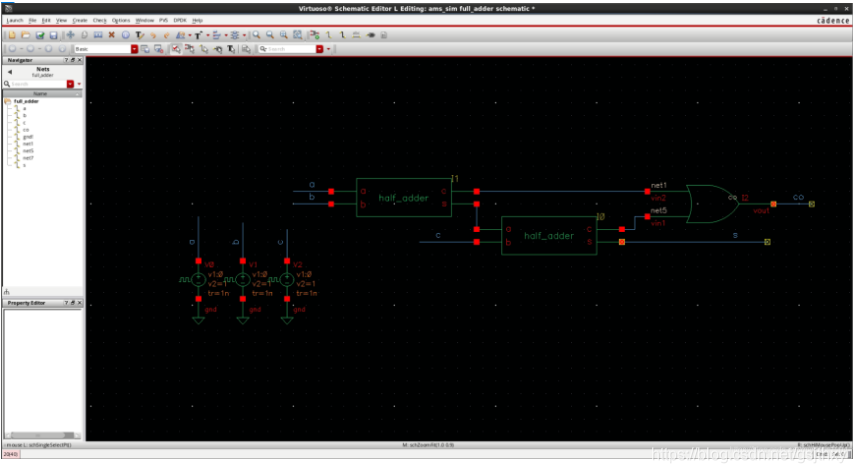

2.2、建立 Analog - Digital 混合仿真原理图

接下来开始进行混合仿真电路原理图的搭建,和建立第一个 Cellview 方法相同,不过在这里 Cell 的名字换成 full_adder 啦,然后记得 Type 这里是 schematic ,相应的 View 会变成 schematic。点击 OK 创建。

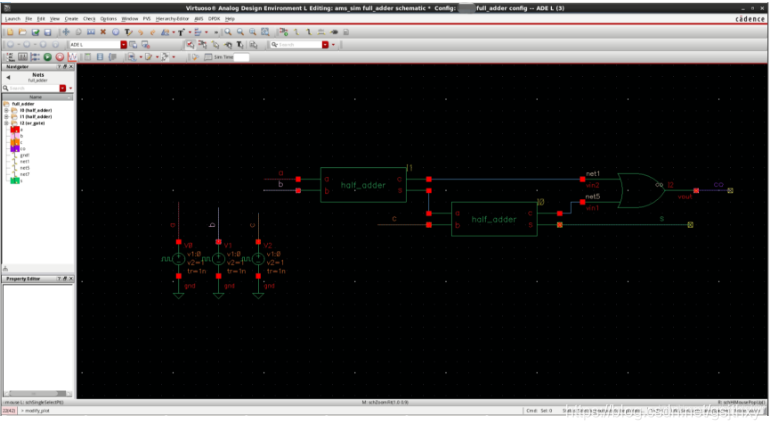

为了方便,使用 ahdlLib 库中的 与门 来代表 Analog 电路。简单放了三个相同的 方波信号源 来模拟 全加器 的输入。绘制完成后,记得 ‘check and save’,然后就可以关掉这个窗口啦。

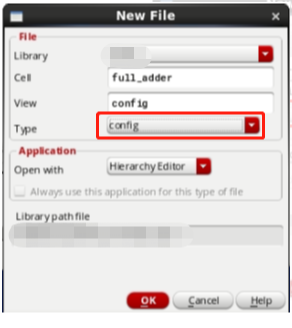

2.3、建立 Analog - Digital 混合仿真config文件

依旧是类似之前创建 Cellview 的方法,不过需要注意的是:这里在 Cell 的名字要与刚刚混合仿真的 schematic的名字相同。Type 一定要选 config。这样在 View 中也是 config。点击 OK 进行创建。

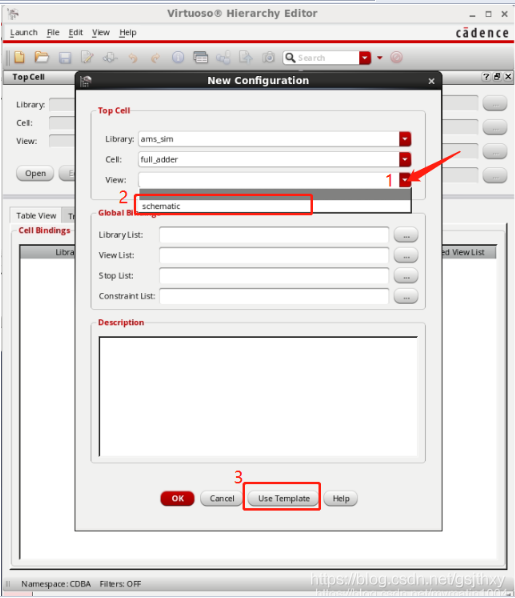

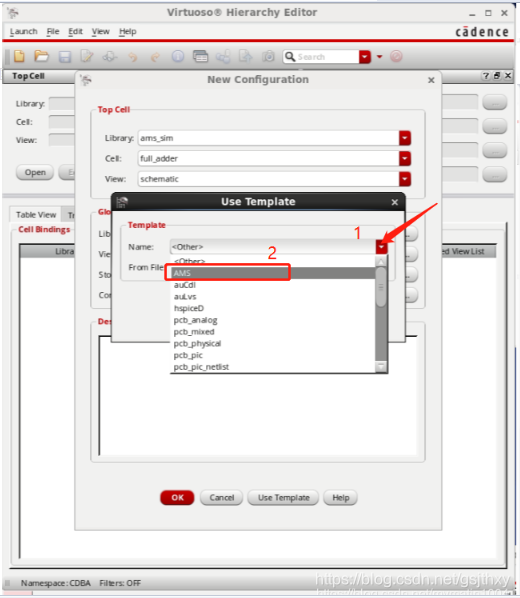

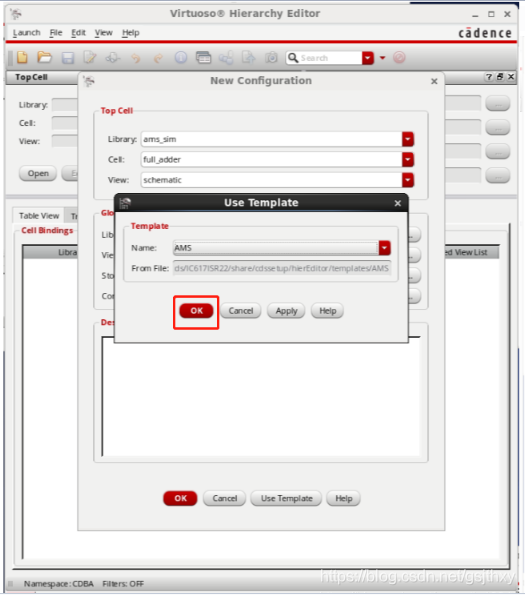

接下来会弹出新的对话框(如下图),首先在 View 中选择 schematic,接下来点击 Use Template (这里就要看大家公司IT部门的兄弟安装软件的给力程度了)。

这时会弹出新的对话框(如下图),在 Name 中选择 AMS。

选好之后点击 OK。

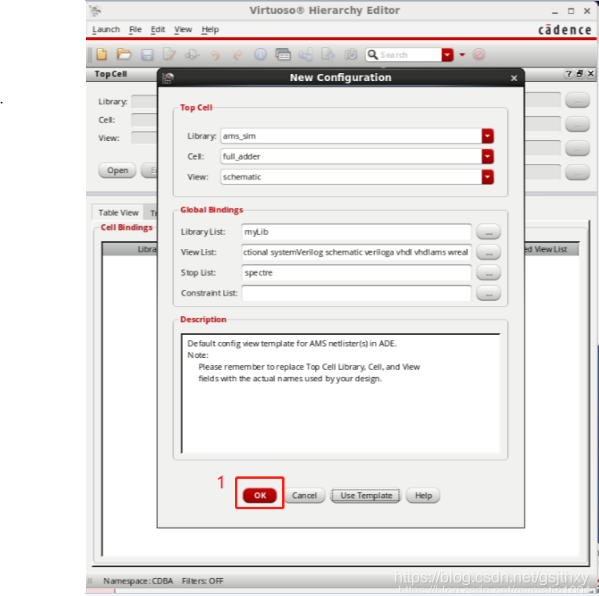

就会发现模板看起来已经加载进来了(如下图),这时点击 OK

2.3、配置混合信号电路仿真环境

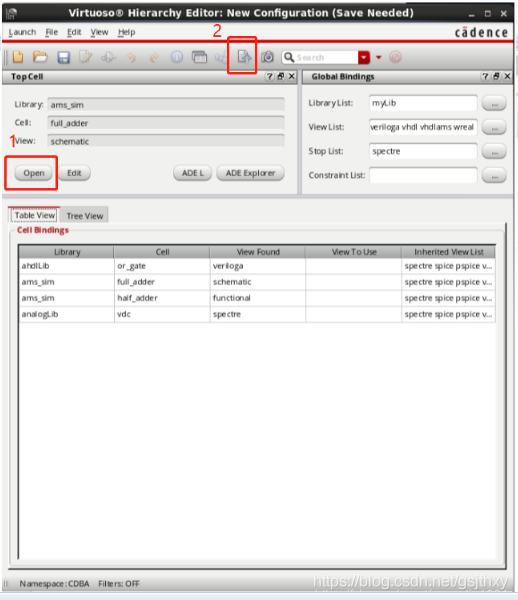

接下来点击 Open 如下图中的 1,这里顺便提一句,下图中的 2 是更新的作用,感觉上类似 schematic 中的 check and save

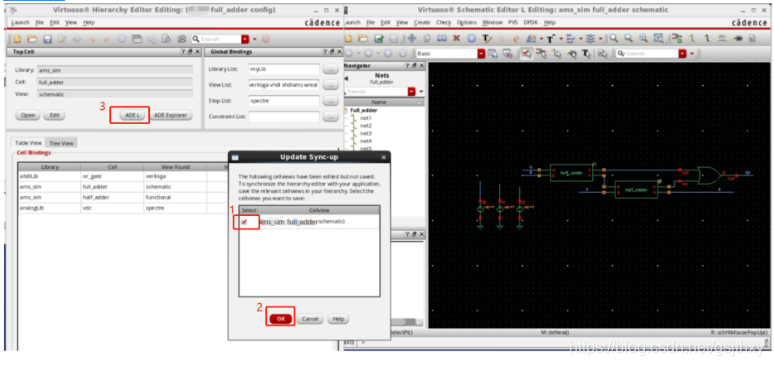

点击完上图中更新的按钮,可能会弹出 Update Sync-up 的对话框,这时记得打钩之后点击 OK就可以啦。接下来点击 3 那里的 "ADE L” 按钮。

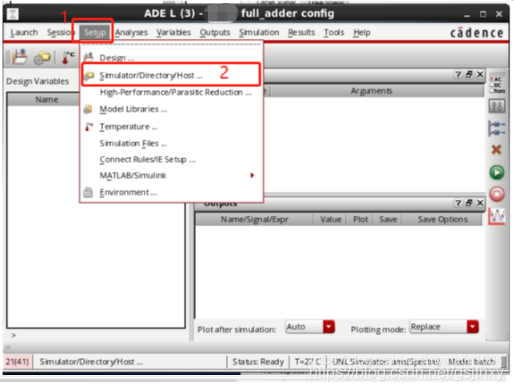

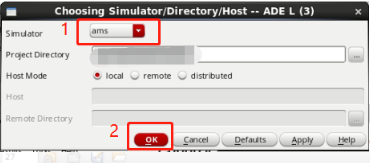

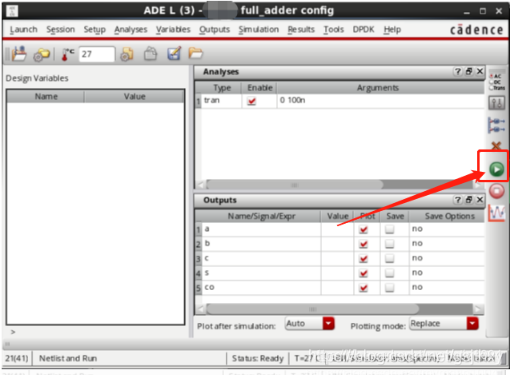

可以发现,ADE L 窗口就出现了(如下图)。这里可以确认一下仿真器是否为 AMS。点击 Setup -> Simulator/Directory/Host…

可以从弹窗中看到 Simulator 是 ams,确认无误之后点击 OK

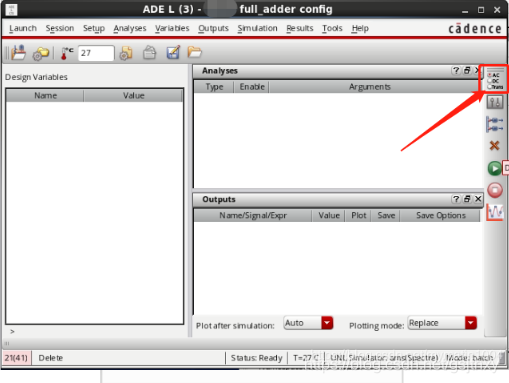

点击按钮(如下图),进入仿真选项界面

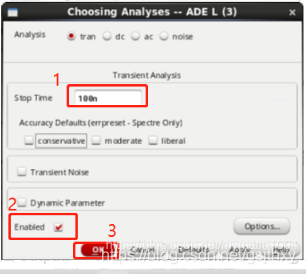

这里进行 tran (瞬态)仿真。这里仿真时间设定为100ns,勾选 Enabled 然后点击 OK

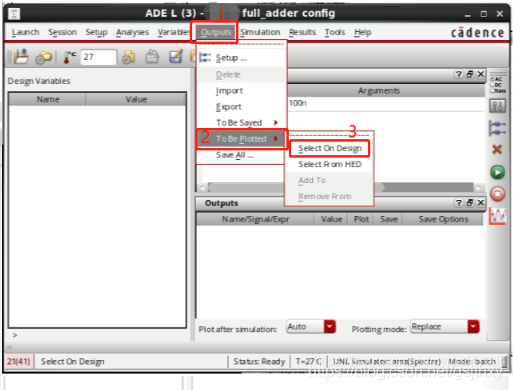

选择仿真之后想要对其绘制曲线的net。点击 Outputs -> To Be Ploted -> Select On Design

这样可以在 schematic 中选择想要绘制其电压信号的 net

Note:选择之后记得按Esc键。

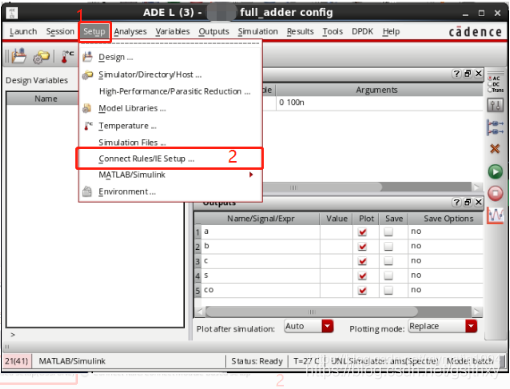

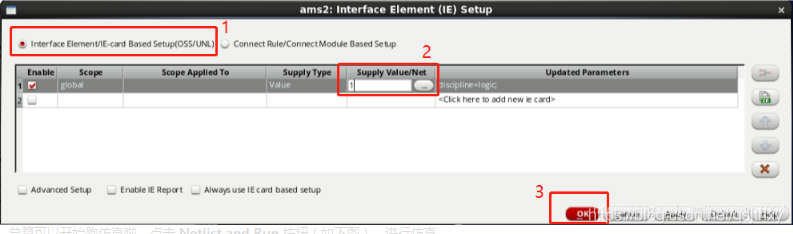

接下来还需要查看一下 Connect Rules (又到体现公司IT部门兄弟实力的时候啦),点击 Setup -> Connect Rules/IE Setup…

可以在弹出的界面中设定 Digital模块的供电电压,这里我假设为1V。设定之后依旧点击 OK

2.4、针对混合信号电路demo进行仿真

总算可以开始跑仿真啦,点击 Netlist and Run 按钮(如下图),进行仿真

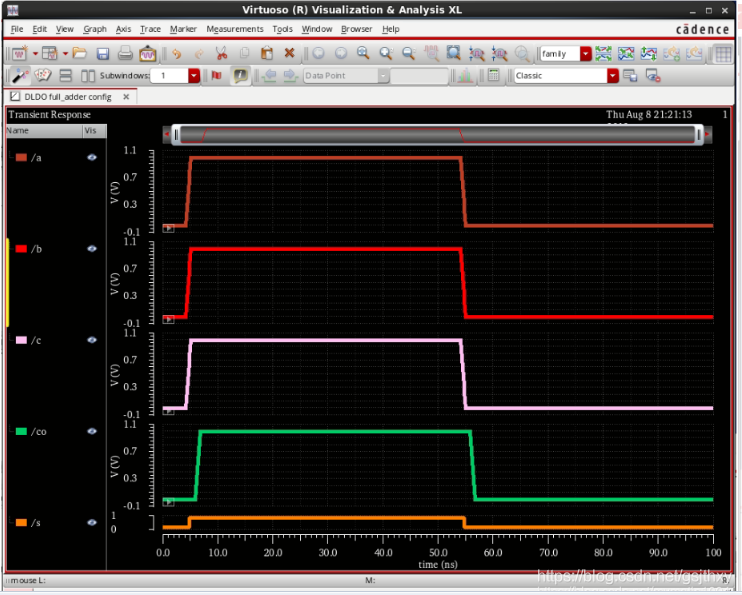

最后的波形如下图所示。不得不说,这个仿真速度确实不是很快,尤其当电路规模较大的时候

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网