日志

利用TDR (时域反射计)测量传输延时

| |

分析方法

本文基于以下三个前提:

1.利用TDR (时域反射计)减小探头误差。TDR通常用来测量信号通路长度与阻抗变化的关系。TDR也是测量传输延2.时的重要工具。

2.避免直接探测。由于加载的原因,有源探头会使测量变得复杂,并引入误差。

3.利用一个实例演示这一方法。本文将以MAX9979为例,该芯片为高速引脚电子电路,适合于ATE系统。芯片内部集成了双路高速驱动器、有源负载以及工作在1Gbps以上的窗比较器。

此处介绍的方法适用于任何高速器件。

TDR原理

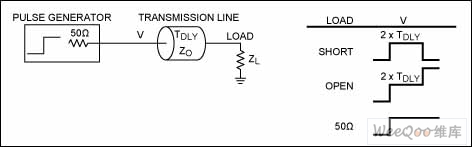

TDR测试方法中,沿信号通路传输高速信号边沿,并观察其反射信号。反射能够说明信号通路的阻抗以及阻抗变化时信号延时的变化,TDR测试的简单示意图如图1所示:

图1. TDR原理,TDR测量基于反射系数ρ,其中ρ = (VREFLECTED/VINCIDENT)。最终,ZO = ρ × (1 + ρ)/(1 - ρ)。从图1可以得到两个重要概念:

1.TDLY是我们将要测量的PCB (印刷电路板)引线延时。

2.ZO是被测PCB引线的阻抗。

仪器和*估板

为了测量纳秒级的延时,需要非常快的脉冲发生器、高速示波器以及高速探头。我们也可以利用具有TDR测量功能的Tektronix? 8000 (图2)系列示波器(TDS8000、CSA8000或CSA8200),配合80E04 TDR采样模块使用。本文采用MAX9979EVKIT (*估板)、Hewlett Packard 8082A脉冲发生器和TDS8000/80E04进行演示。图3所示为MAX9979EVKIT部分电路。可以选择使用任何具有TDR功能的高速示波器和任何高速差分脉冲发生器,同样能够获得相似结果。

图2. Tektronix TDS8000系列具有采样模式的示波器

图3. MAX9979EVKIT (部分)

分析中将进行以下测量:

1.从PCB的SMA边缘连接器DATA1/NDATA1至MAX9979 IC输入引脚DATA1/NDATA1的延时。从MAX9979的DUT1 (被测器件)输出通过SMA连接器J18的延时。

2.连接DUT1输出至CSA8000的测试电缆延时。

3.从DATA1/NDATA1输入至DUT1输出,通过电缆到达CSA8000的总延时。

4.最后,计算MAX9979的实际延时。

DATA1/NDATA1输入建模

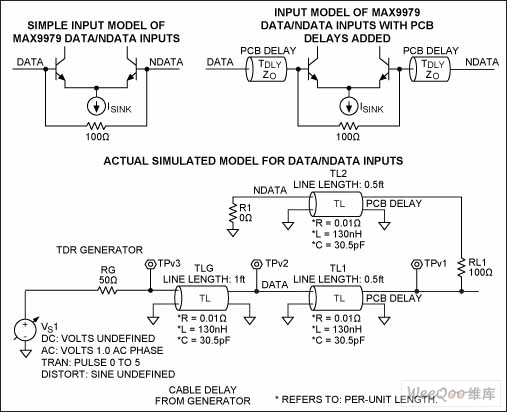

由于人们对TDR响应比较困惑,我们首先利用SPICE仿真器构建输入延时的模型。然后我们将仿真结果与实际测量进行比较,参见图4。

图4. 等效输入原理图和最终仿真模型

图4注释:

1.PCB引线设定为6in长,阻抗为65Ω。实际上,这是DATA1/NDATA1 PCB引线的真实阻抗。理想情况下为50Ω,但我们从TDR测量结果将会看到该值为63Ω。

2.NDATA1输出端接至地。由于DATA1和NDATA1对称,而且距离MAX9979引脚的长度相同,所以仅测量DATA1的PCB引线。

3.对信号发生器的12in电缆进行建模,但实际传输延时测量证明并不需要这一建模。

DATA1/NDATA1输入仿

图5所示为TPv3的SPICE仿真波形。

图5. 图4所示模型的SPICE仿真(节点TPv3),在MAX9979EVKIT DATA1输入采集到的数据。

从图5数据可以得出以下几点结论:

1.输入信号为阶跃函数。这次仿真中,阶跃幅度为0.5V。以此模拟CSA8000产生的TDR信号。

2.时间代表模型中不同单元的延时:

a.第1级表示发生器的12in电缆。延时大约为3ns,是实际延时的两倍。实际电缆延时为1.5ns。

b.第2级表示DATA1 PCB引线。延时大约为2ns,PCB延时为该值的一半,或1ns。

c.其它延时为脉冲通过DATA1 PCB引线的反射。

3.Y轴反映了不同元件的阻抗,单位为伏特,可转换为阻抗。

4.X轴为单次输入阶跃信号造成的模拟信号反射,参照图1对信号进行比较。这些信号的长度代表通过不同元件的延时。

MAX9979的传输延时测量

按照以下六个步骤进行传输延时测量。

第1步:测量连接DUT1节点到CSA8000垂直输入的2in长SMA电缆的延时(图6)。

图6. 2in SMA电缆的CSA8000 TDR

测量时:

1.将2in长SMA-SMA电缆连接至80E04 TDR模块的一路输入,另一端保持开路。

2.利用TDR的下拉菜单进行测量。

3.注意,这看起来很像图1中的“开路”示例。此处测得的延时为804ps,由于是两倍的电缆延时,所以电缆延时为402ps。

4.还需注意的是,第2级阶跃实际为顶部和底部之间的一半。根据TDR原理,表示2in长度电缆实际阻抗为50Ω。

5.这条2in电缆是我们测量延时的通路之一。

第2步:测量DATA1输入信号的PCB引线延时/阻抗。

图7. DATA1 PCB TDR阻抗测量

从该数据可以获得以下几项信息:

1.图7与图5中的仿真曲线相同,证明了模型的准确性。

2.光标用于测量线路阻抗。第1级阶跃为49.7Ω,代表CSA8000电缆。与我们的预期结果一致。

3.第二光标显示97.8Ω,为MAX9979内部DATA1/NDATA1两端的100Ω电阻(参见图4)。与我们的预期结果一致。

4.第2级阶跃阻抗不是50Ω。这一级为DATA1 PCB阻抗,大约为63Ω。这意味着DATA1和NDATA1的PCB引线不是我们所希望的50Ω。

5.大幅值为150Ω,是额外的50Ω电缆和100Ω电阻,只存在于第3级反射。

该测量可以简化为:

1.将12in SMA电缆的一端连接至CSA8000。将电缆另一端连接至MAX9979EVKIT的DATA1 SMA输入连接器。

2.将NDATA1的SMA连接器通过SMA接地,从图4可以看出这一点。12in SMA电缆的长度与延时测量无关,但应尽可能短。

3.无需对MAX9979EVKIT供电。该测量针对焊接到电路板上的MAX9979进行,但不需要上电。有些用户更喜欢使用没有焊接器件的电路板进行测量。断开MAX9979将产生更清晰的3级阶跃信号,仿真图1所示开路状态。两种配置下,实际时间测量结果相同。

图8. 波形与图7相同,但为扩展后的波形,测量延时。

图8所示,测量第2级阶跃—DATA1 PCB引线延时。注意:

1. 第1级阶跃为电缆,我们对其延时并不感兴趣。

2.测量值为1.39ns,PCB延时为该值的一半,或为0.695ns。这一延时确实大于模型的延时,但我们仅利用模型估算延时加以比较。

3.测量在信号的倾斜沿进行。这些倾斜沿代表电路板SMA和MAX9979 DATA1引脚的电容效应。因此,在这些倾斜沿之间进行测量能够确保测试结果包含了SMA和PIN延时。还需注意的是,波形中存在凸峰:这是SMA连接器与电路板之间的电感产生的。由此,需要在凸峰之前进行测量,以确保获取完整的电路板延时。进一步的TDR测量读数将突显这些电容和电感造成的倾斜沿和凸峰。

第3步:测量DUT1输出信号的PCB引线延时/阻抗。

图9. DUT1 PCB TDR延时和阻抗测量

图9所示示波器波形是采用与图7、图8相同的设置产生的。我们现在采用一条2in长SMA电缆连接CSA8000 80E04模块MAX9979EVKIT的DUT1 SMA。注意:

1.第1级阶跃表示2in电缆。TDR信号为0.5V,第1级阶跃为250mV。说明我们电缆的阻抗为50Ω,与预期情况一致。

2.DUT1延时是在两个倾斜沿之间进行测量得到的,与上述DATA1测量说明相同。然而,需要注意的是:这些倾斜沿之间的电平同样为50Ω。该值表明较短的DUT1 PCB金属线非常接近于理想的50Ω。

3.从上述内容得到DATA1引线阻抗为63Ω,DUT1节点阻抗为50Ω。这意味着DATA1输入的金属线宽比DUT1输出的线宽窄。理想情况下,它们应该相同。TDR测量发现了这一差异,这不一定是系统错误。DUT1引线阻抗稍高是由于较窄的金属线造成的,但它同时也减小了DATA1金属线的电容。数据线是最长的引线,为了保证最宽频带的要求,该电容应尽小。

4.DUT1的PCB延时很难测量,其阻抗与电缆相同。如果MAX9979没有焊接到电路板上,我们将看到“开路”状态的三级阶跃信号。但是,在焊接了MAX9979的条件下仍然可以测量到这一延时。通过检查电容效应产生的倾斜沿,可以看出SMA连接器在电路板的焊接位置以及MAX9979 DUT1引脚的位置。我们同样可以查看SMA连接器电感产生的凸峰,确认它处于两个倾斜沿之间。解决了这些问题,可以测得延时为360ps,将该值减半,得到实际DUT1 PCB电路板的延时,该延时为180ps。

第4步:用两条相同的SMA电缆连接差分信号发生器,测量CSA8000的基线延时。

图10. 测量来自发生器的DATA1/NDATA1信号

图10所示,C1和C2是两个互补PECL信号,幅值大约为450mV。这些DATA1和NDATA1信号直接由外部的信号发生器产生,送入CSA8000输入。我们采用CSA8000的20GHz采样探头,从该数据可得出以下结果:

1.M1是差分信号C1 - C2的数学计算值,幅值为900mV,10%/90%上升和下降时间接近于700ps。这意味着DATA1/NDATA1信号上没有任何干扰。

2.我们还对Crs或M1差分信号的过零点进行测量,测得数据为29.56ns。触发示波器,我们仅关注这些过零点中的一个。给MAX9979上电,然后测量相同过零点,因为它是通过整个电路板的延时。

3.该延时还包括两条输入电缆的延时,因为这些电缆也被用于测量通过电路板的信号延时,其延时相互抵消。尽管如此,最好还是使用尽可能短的电缆,只是该延时对传输延时测量并不重要。

第5步:MAX9979EVKIT上电。

图11. MAX9979上电并为CSA8000的50Ω负载产生3V信号

将DATA1和NDATA1信号连接至已上电的MAX9979EVKIT的DATA1/NDATA1输入。使用与第4步相同的电缆。按照传输延时测量技术资料的规定,将MAX9979设置为规定的0V至3V信号,并将输出端接至50Ω。本例中,50Ω负载为CSA8000输入,从图11获得的数据点显示:

1.当前的输出信号幅值为0V至1.5V,与预期情况一致,由于50Ω负载的存在而被除以2。

2.上升和下降时间完全在MAX9979的技术指标范围内。由此,我们可以确认由干净、有效的DATA1/NDATA1驱动产生完好、干净、有效的输出。

3. CSA8000保持与第5步相同的设置,触发方式与第4步相同。我们可以看到过零点为33.77ns。

第6步:计算MAX9979的传输延时。

通过MAX9979EVKIT的总延时为:

33.77ns - 29.56ns = 4.21ns

计算测量结果:

1.减去0.695ns的DATA1 PCB引线延时,所得延时为3.515ns。

2. 减去0.18ns的DUT1 PCB引线延时,所得延时为3.335ns。

3.减去CSA8000的2in电缆延时,该延时为402ps,所得延时为2.933ns。

MAX9979技术指标中,这种配置下的标称延时为2.9ns。这里,我们可以得到焊接了MAX9979的*估板的延时为2.933ns,非常接近于预期值。

总结

1.以上分析表明利用TDR测量传输延时具有以下优势:

2.传输延时测量结果非常准确。

3.无需有源探头(避免由此引入的误差)。

4.简单技巧可用于绝大多数传输测量。

5.阻抗测量保证正确的连接器和PCB引线阻抗。

6.利用TDR信号能够分析信号通路的附加电容和电感,必要时可作为重新设计的反馈信息。

7. 简化模型和仿真工具确保获得正确结果,并可验证测量配置。

8.采用良好的测试方法测量关键指标。

随着信号速率的提高,时序测量的误差和错误会造成不正确的电路规划、器件选择及系统设计。高速测量中保持良好的方法能够避免亡羊补牢造成的损失。本文着重强调了这些良好的设计习惯。 (中国电子应用网)

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网