日志

发表评论 评论 (5 个评论)

- 回复 hebut_wolf

- 按照analog的思维,相同位宽顶多降低3dB snr(我是11bit 精度的adc)

knowworlds: 额,这个不是因为你实际data肯定是有bit位数的么,那么数字域做处理的时候再怎么样不能比你原本的bit位宽小吧,不然天然就降SNR了?我是这么理解的,看老哥你是 ...

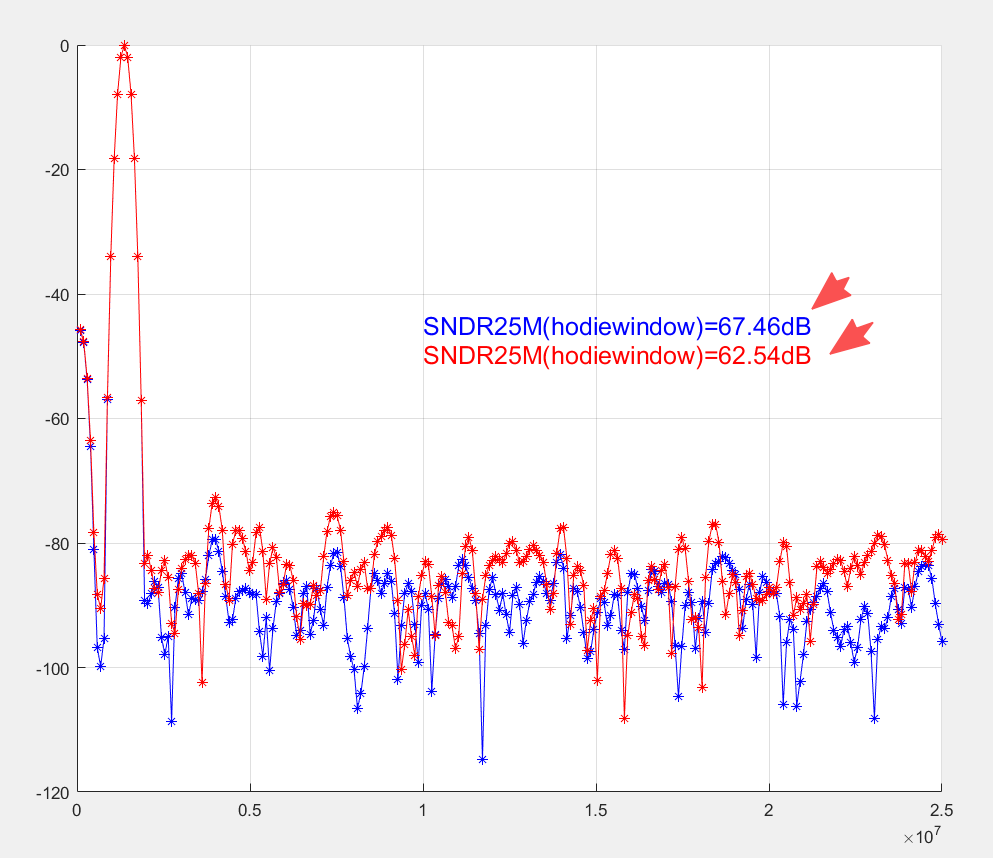

我们实现出来降低了6dB,这些多余的噪声我没理解是怎么来的,怎么评估(我附上了图)

那个蓝色的是13bit位宽 红色的是11bit位宽(第一张图)(我是ns sar)

- 回复 knowworlds

- 额,这个不是因为你实际data肯定是有bit位数的么,那么数字域做处理的时候再怎么样不能比你原本的bit位宽小吧,不然天然就降SNR了?我是这么理解的,看老哥你是做ADC的,应该比我懂呀。

hebut_wolf: 我们设计的时候没有2bit小数 所以sndr达不到7bit

rx 也是这样,会恶化adc data的sndr,确实增加位宽就好了

我不知道这里面的原理是啥 ...

- 回复 hebut_wolf

- 我们设计的时候没有2bit小数 所以sndr达不到7bit

knowworlds: 你说的是什么意思,我不是很理解。我举个例子,对于现在高速serdes中的TX,使用的是DAC架构,其TX FFE本质就是数字FIR滤波器。一个7bit DAC,TX FFE在数字域计算 ...

rx 也是这样,会恶化adc data的sndr,确实增加位宽就好了

我不知道这里面的原理是啥

- 回复 knowworlds

- 你说的是什么意思,我不是很理解。我举个例子,对于现在高速serdes中的TX,使用的是DAC架构,其TX FFE本质就是数字FIR滤波器。一个7bit DAC,TX FFE在数字域计算的时候,用的是7bit整数+2bit小数的计算。最终四舍五入截断到7位整数后喂给TX,这种FIR应该不会导致滤波效果很差把?

- 回复 hebut_wolf

- 如何确定最佳位宽,我认为跟fir滤波器系数的位宽相等就可以了,如果位宽要折中,迭代两次即可

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网