日志

ESD(Electrostatic dischage) Protection

| ||

Introduction

摩擦起电(triboelectric effect)等导致ESD。

ESD: 具有大量积聚电荷的导体向另一个相对低电势的导体进行放电(ESD event),两者的电势差可能高达数kV,通过短时间高脉冲样波形冲激电路,只需要一小部分电势差就能够让一个不受ESD保护的电路损毁(栅氧化层击穿、热损毁、金属层融化、金属击穿或者接触孔损毁)或者改变电路特性(例如V_{th}发生偏移)。

防护的方法在于通过并联于受保护电路的方式,将电荷通过低阻抗路径(<2Ω)泄放。

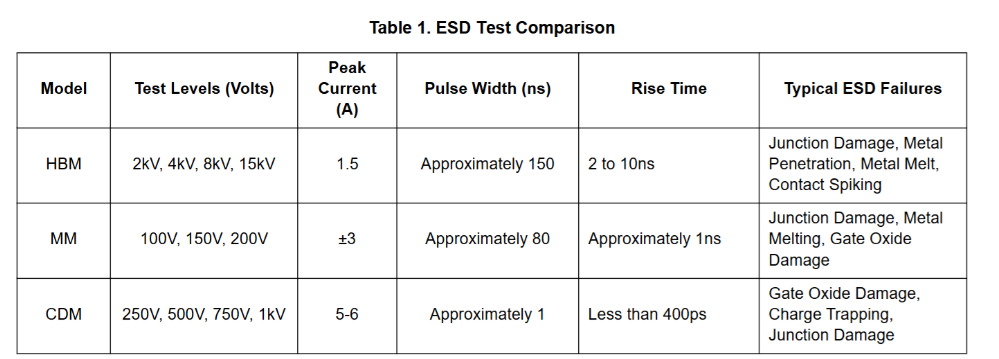

模型

ESD specifications of human-body model (HBM) of ±2kV, machine-model (MM) of ±200 V , and charged-device model (CDM) of ±1kV

人体放电模型(Human-body model)

Values for the high-voltage supply vary according to the test level between 0.5kV and 15kV.[5]

机器放电模型(Machine model)

Traditional values for the high voltage supply can vary, but the most common range from 50V up to 400V.[5]

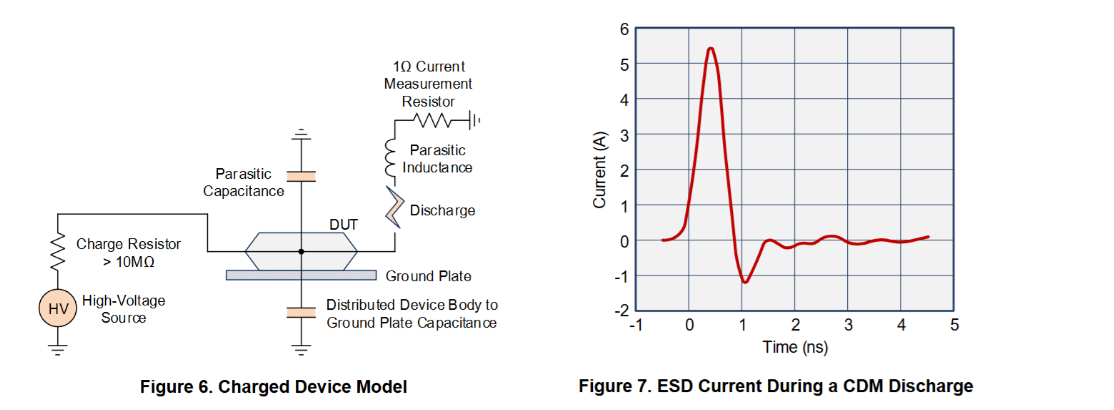

充电器件模型(Charged-device model)

在封装好的芯片上的静电荷。

模拟自动化生产环境中常见静电放电情形。在这种自动化环境下,机器通常长时间持续运行,这会导致电子IC逐渐积累电荷。当带电的芯片接触到接地的导体时,器件上积累的电荷(相当于残余电容)会迅速放电——这就是CDM要模拟的情况。

测试步骤说明:

待测芯片(Device Under Test, DUT)被正面朝上放置在测试板上。

形成电容结构:在芯片下方有一块金属平板(field plate),中间隔着一层绝缘材料。这层绝缘体使金属板与芯片之间形成一个电容结构。

充电过程:金属板连接到一个高压电源,电压被升至规定的CDM测试电压。这样,DUT(芯片)就像一个被充电的电容器。

放电过程:一个接地的探针接近芯片上某个引脚时,电荷通过该引脚迅速放电。这个放电事件会被监测,以确认静电放电(ESD)确实发生。

重复测试:每个引脚都会经历3次正向脉冲和3次负向脉冲,一共 6次放电。

ESD电路设计方法

ESD电路必须具有快速(响应迅速、距离Pad近)泄放(低阻抗<2Ω、瞬间高电流承载力>100mA、倒角处理防止局部过高场强、面积大散热好寄生大),同时不影响现有的电路(influenceability、信号速度、并联与受保护电路)。

ESD design window

对于No snap back(折返特性)的ESD电路,VBD (例如diode的Von,VBD=VDD+Von)应该小于损毁电压、接近Safety margin;对于snap back的电路,Vt1 应该小于损毁电压,Vh 应该接近Safety margin。最后一段都是低电阻的曲线斜率,将电压"钳位"到VBD/Vh附近。ESD电路应该设计得不让自身损毁,例如只进入雪崩击穿而不是热损毁。具有Snap-back特性的ESD电路优点在于(1) 能够将电压钳位到更低的位置,更小的热损毁风险(IV乘积更小)

任意两个点之间的电压就是(最大的时候是PP或者NP模式,忽略了Zenar Diode的压降)

ESD Protection Circuit

1. 面积大

2. 距离Pad近

3. 直角走线做倒角处理

Gate oxides can withstand a field strength of approximately 1 V/nm, according to [22]. They are vulnerable at a few volts (in advanced nm-CMOS processes <20 nm) as they are only a few nm thick. 需要两级ESD保护电路.

确定ESD设计窗口,Vor-VDD,其中Vor是oxide rupture电压即栅氧化层损毁电压。

第一级ESD电路将电压钳位到V1,然后第二级电路将电压钳位到更小的V2。

电阻的两个作用(1)限制放电电流I2的峰值,电阻R设置得比D1的导通电阻大得多从而限流,D2可以做的很小(2) 电阻R比D2的导通电阻大得多使得压降主要由R承担,Vr>>V2。

电阻的副作用处于信号通路上,高阻值会降低电路的响应速度。

ggNMOS电路也可以用来替换Diode。实际上二极管作为ESD保护器件已经不常用。

ggNMOS(Gate-grounded NMOS),在Pin(也就是Drain端)输入负脉冲的时候,Bulk到Drain的PN结(DB二极管,DB diode)导通,从地吸收正电荷/电流;在Pin输入正脉冲的时候,Drain和Bulk组成的PN结反向导通(也就是雪崩击穿),正电荷积聚在寄生NPN(MOS的Drain-pSub-Source)的基极(阱电阻比较大)使得VBE>VON,寄生NPN导通建立起从Drain/Collector到Source/Emitter(不经过沟道)的低阻抗路径,Pin的电压下降、雪崩击穿恢复,正电荷继续短暂积聚在NPN的基极,使得后者持续导通。

ggNMOS的Drain一般要做的足够宽,并且Metal到OD的Via距离Gate较远,构成一个限流电阻Rbal ,防止过大的电流导致热损毁。一般可以通过SAB-Block在Drain上形成没有salicide的高阻区域,多插指的MOS管使得每个finger都能均匀分流。

RC Protection Circuit

ESD第一级电路距离PAD近,第二级电路RC clamp电路距离内部受保护电路近。

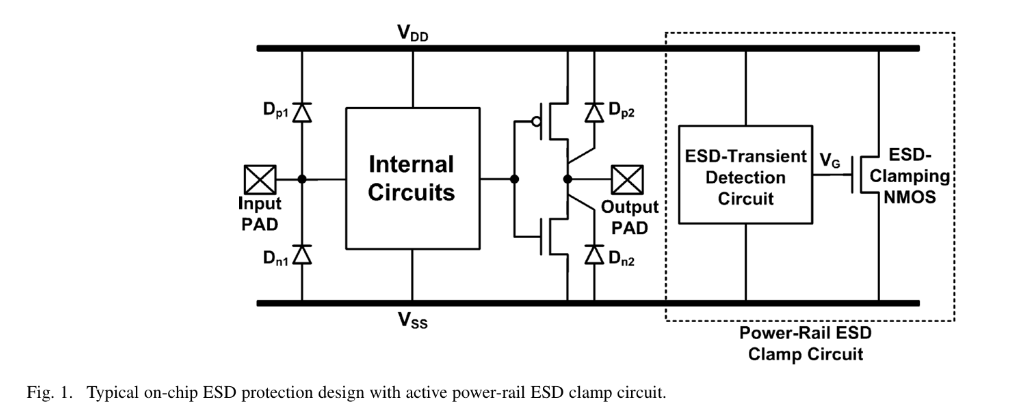

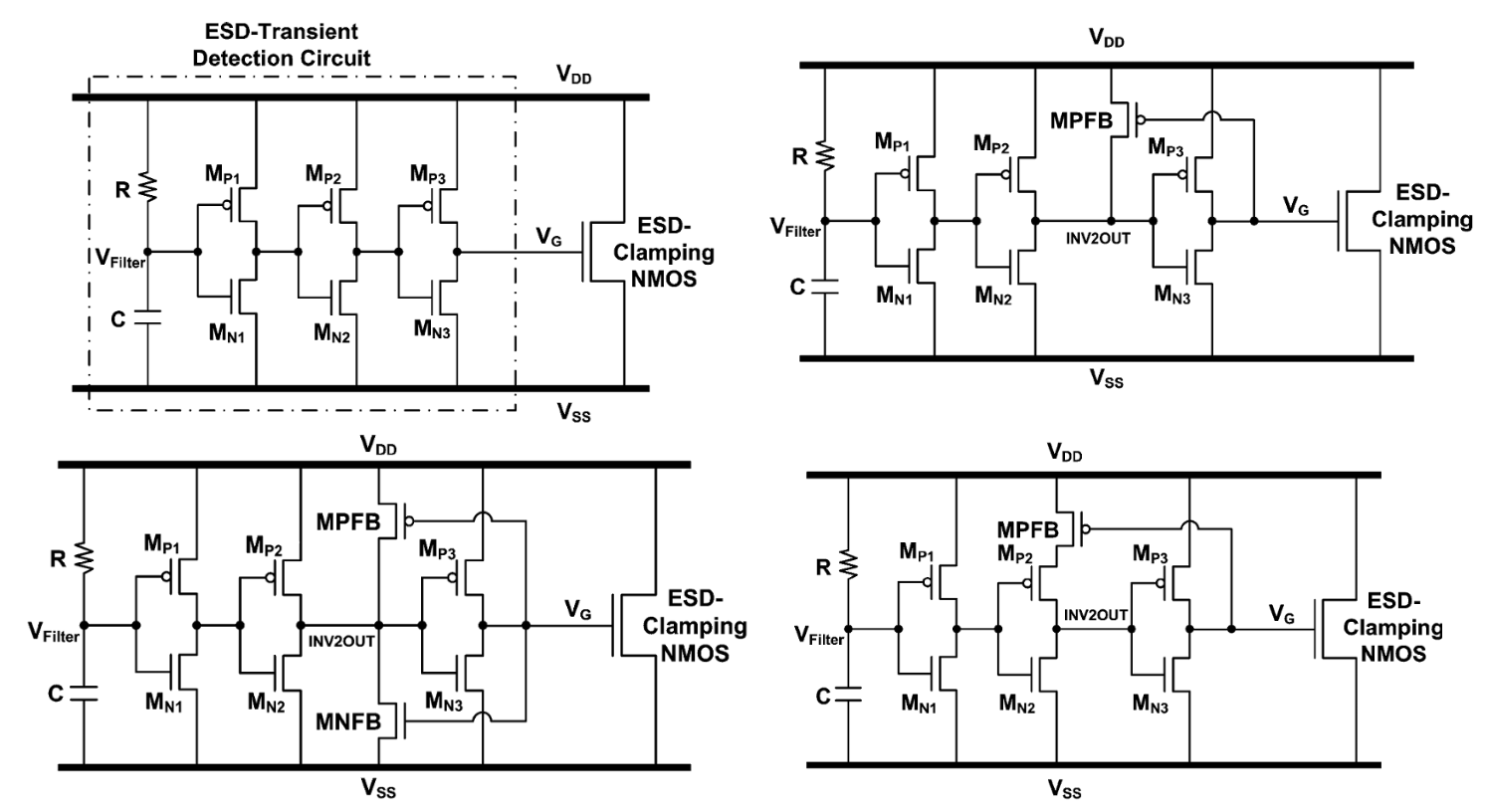

active power-rail ESD clamp circuit

[1] Fig. 2. Four different power-rail ESD clamp circuits designed with (a) typical RC-based detection, (b) PMOS feedback, (c) NMOS+PMOS feedback, and (d) cascaded PMOS feedback.

ESD-clamping NMOS用来给VDD和VSS之间提供低阻抗通路来泄放ESD电流。

Discharged model

P表示正脉冲,N表示负脉冲;第二个字母,D表示以VDD为参考地,P表示以Pin为参考地,S表示以VSS为参考地。PD和NS经过的Diode最少,PP和NP经过的Diode最多。

example: 当Pin的电压高于VDD一个Von时候,Ddi 导通,电荷通过VDD路径,然后通过齐纳二极管泄放(因为试图拉高VDD的电压,但是齐纳二极管反偏时候电阻非常小,非常大的电流才能拉通DDS )到地。

ESD in different power domain

高速信号的考虑

1. 电压钳位、电荷储存能力

2. 对射频信号的影响

To avoid unexpected ESD damages in the internal circuits under pin-to-pin and-to ESD stresses, the power rail ESD clamp circuit must be designed with high turn-on efficiency and fast turn-on speed. [1]

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网