日志

详细资料 | 时钟缓冲器及发生器9ZXL0851AKLF 9ZXL0853EKILF 9FGV0841AKLF 9FGV0841AND ...

| |||

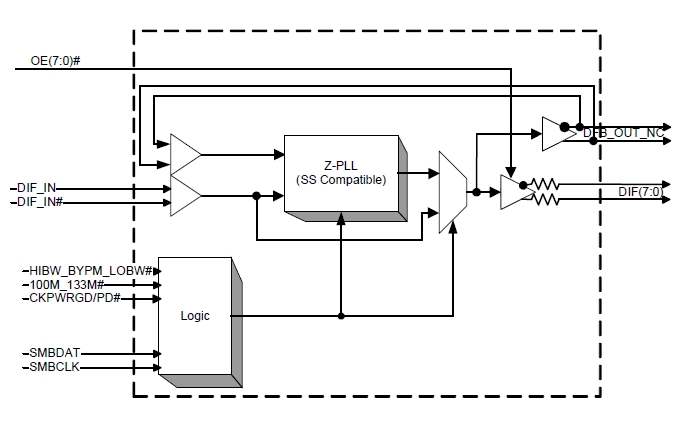

1、9ZXL0851AKLF是一款低功耗8路输出差分缓冲器,符合Intel DB1200ZL规范的所有性能要求。它适合PCI-Express Gen1/2/3或QPI/UPI应用,并使用固定的外部反馈来保持低漂移,以满足苛刻的QPI/UPI应用。具有以下特性:

8至0.7V低功耗HCSL兼容输出对

Zo =欧姆的低通HCSL输出;节省功耗和电路板空间——无需端接电阻。

节省空间的48引脚VFQFPN封装

0ps输入至输出延迟的固定反馈路径

8个OE#引脚;每个输出的硬件控制

PLL或旁路模式;PLL可以消除输入时钟的抖动

100MHz或133MHz PLL模式操作;支持PCIe和QPI应用程序

可选PLL带宽;将下游PLL的抖动峰值降至最低

扩频兼容;跟踪扩展输入时钟以实现低EMI

周期间抖动< 50ps

输出间偏斜< 65 ps

输入至输出延迟变化< 50ps

PCIe第三代相位抖动< 1.0ps RMS

QPI/UPI 9.6GT/s 12UI相位抖动< 0.2ps RMS

应用领域

9ZXL0851AKLF主要适用于 AMD Genoa 的完整电源和时序系统,支持 SVI3、DDR5 和 PCIe Gen 5/6。

2、9ZXL0853EKILF是一款符合PCIe gen 1–5标准的增强型差分时钟缓冲器。该器件支持复杂的时钟架构,如SRIS和SRNS。固定的外部反馈为关键的QPI/UPI应用保持低漂移。9ZXL0853EKILF具有SMBus写锁定功能,可提高设备和系统安全性。9ZXL0853EKILF还具有多达9个可选的SMBus地址。

9ZXL0853EKILF主要特性如下

符合PCIe Gen1–5标准

SMBus写保护功能;提高系统安全性

合众国际社/QPI支持

支持PCIe SRIS和SNRS时钟

85ωZout低通HCSL输出;每个输出对消除4个电阻

8个OE#引脚;每个输出的硬件控制

9个可选SMBus地址;多个设备可以共享同一个SMBus网段

可选PLL带宽;将级联PLL拓扑中的抖动峰化降至最低

PLL带宽和旁路的硬件/SMBus控制;改变模式而不重启

扩频兼容;跟踪扩展输入时钟以降低EMI

100MHz和133.33MHz ZDB模式

6mm × 6mm 48-VFQFPN封装;小电路板尺寸

应用场景

服务器/高性能计算

nVME 存储

网络

加速器

工业控制

3、9FGV0841AKLF是一款8路输出极低功耗时钟发生器,适合PCIe Gen1–4应用,集成输出端接,提供Zo = 100电阻。该器件具有8个时钟管理输出使能,除了扩展外,还支持2种不同的扩频电平。

9FGV0841AKLF具有以下特性:

符合PCIe Gen1–4标准

集成终端提供100ω差分Zo:减少元件数量和电路板空间

1.8V工作电压:降低功耗

输出可以选择从1.05V到1.8V之间的任何电压供电:最大限度地节省功率

OE#引脚:支持DIF电源管理

LP-HCSL差分时钟输出:降低功耗和电路板空间

各输出的可编程压摆率:允许针对各种线路长度进行调谐

可编程输出幅度:允许针对各种应用环境进行调谐

DIF输出被阻塞,直到PLL被锁定:干净的系统启动

DIF输出上可选的0%、-0.25%或-0.5%扩展:降低EMI

外部25MHz晶体;支持紧密ppm,合成误差为0ppm

配置可以通过捆扎引脚完成:设备控制不需要SMBus接口

3.3V兼容SMBus接口支持传统控制器

节省空间的6 × 6 mm 48-VFQFPN;最小的电路板空间

可选的SMBus地址:多个设备可以轻松共享一个SMBus网段

提供通过AEC-Q100认证的2级(-40°C至+105°C)版本(可润湿侧翼封装)

典型应用

▪ 转接卡的 PCIe Gen1–4 时钟生成

▪ 存储器

▪ 网络

▪ JBOD的

▪ 通信

▪ 接入点

4、9FGV0841ANDG2是一款适合PCIe Gen1–4应用的时钟发生器,它集成输出端接,提供Zo=100 ohms。9FGV0841ANDG2具有8个时钟管理输出使能,除了扩展外,还支持2种不同的扩频电平。主要特性如下:

符合PCIe Gen1–4标准

集成终端提供100ω差分Zo:减少元件数量和电路板空间

1.8V工作电压:降低功耗

输出可以选择从1.05V到1.8V之间的任何电压供电:最大限度地节省功率

OE#引脚:支持DIF电源管理

LP-HCSL差分时钟输出:降低功耗和电路板空间

各输出的可编程压摆率:允许针对各种线路长度进行调谐

可编程输出幅度:允许针对各种应用环境进行调谐

DIF输出被阻塞,直到PLL被锁定:干净的系统启动

DIF输出上可选的0%、-0.25%或-0.5%扩展:降低EMI

外部25MHz晶体;支持紧密ppm,合成误差为0ppm

配置可以通过捆扎引脚完成:设备控制不需要SMBus接口

3.3V兼容SMBus接口支持传统控制器

节省空间的6 × 6 mm 48-VFQFPN;最小的电路板空间

可选的SMBus地址:多个设备可以轻松共享一个SMBus网段

提供通过AEC-Q100认证的2级(-40°C至+105°C)版本(可润湿侧翼封装)

典型应用

转接卡的 PCIe Gen1–4 时钟生成

存储器

网络

JBOD的

通信

接入点

全部作者的其他最新日志

- • UltraCMOS® PE4314B-Z射频数字步进衰减器 / TCAN4550RGYRQ1 TCAN1051GDRQ1 TPS62876QWRZVRQ1 汽车级集成电路(IC)

- • 支持 2 通道、3 通道电荷共享的TPS65197BRUYR 8 通道电平转换器 / TPS65126RSHR / TPS27S100BPWPR 详细参数

- • 面向SiC MOSFET的MGD3160AM515EKR2高压栅极驱动器 ADSP-21489BSWZ-4B ADS7952SBDBTR PM8532B-F3EI

- • 1 至 20 路 HCSL 扇出缓冲器ZL40294LDG6 A1104LLHLT ADSP-BF706KCPZ-4 400MHz BLACKFIN+嵌入式处理器资料

- • 具有 SENT 输出的汽车压力传感器信号调理芯片 RAA2S4267B5HSP RAA2S4266B5HSP RAA2S42 ...

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网