日志

2023-08-22

| |

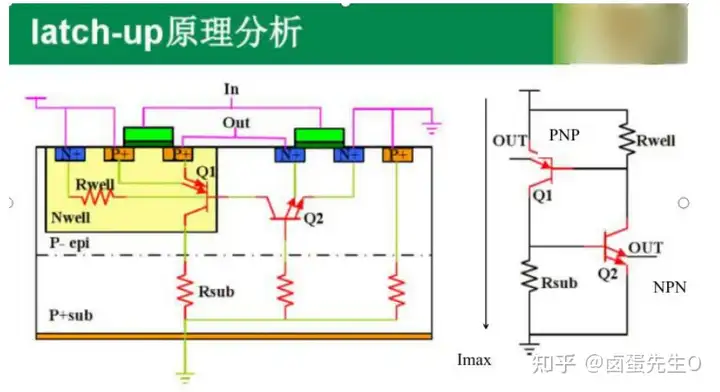

假设电源是VDD,地是VSS,当out信号的电压高于VDD+0.7V,BJT Q1 PN节正偏,Q1 将被打开,或者当out的电压低于VSS-0.7V,BJT Q2 PN节正偏,Q2 将被打开,Q1和Q2 的基级连接了对方的集电极,形成了一个正反馈的回路,经过多轮正反馈,NW和PW出现了一条低阻抗的通路,导致VDD和VSS之间出现大电流,永久性损坏MOS管。

全部作者的其他最新日志

- • 金属连线

- • 2023-09-19

- • SKILL

- • SKILL 取list里面相隔的元素

- • LATCH UP基础知识

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网