日志

封装基板出厂100欧姆,测试85欧姆?

| |

作者:一博科技高速先生成员 陈亮

封装基板(Package Substrate)是半导体芯片的载体。为芯片提供连接、保护、支撑、散热、组装等功效,以实现多引脚化,缩小产品体积、改善电性能及散热性、多芯片模块化等。我们生活中看到的芯片基本都是已经装载在封装基板上了,且基本都有外壳保护,只有一小部分会使用chip on board工艺直接实装在PCB板上。

可能有小伙伴就要问了,我是做设计或者仿真的,有必要知道芯片用什么封装外壳吗?对此我只想说:‘肥肠’有必要哇!

不光你不信,雷豹也不信。

测试@来福:雷豹,芯片上走在表层的100欧姆高速信号,只有85欧姆,你个扑街是不是设计错了?

设计@雷豹:表层高速信号都检查过,都是100欧姆莫问题啊,是不是常威那个扑街加工错了?

板厂@常威:靓仔,饭可以乱吃,话不能乱讲,要用事实说话,我这边阻抗测试是很好的喔,你们不信就测试下备份的光板。

测试@来福:光板表层阻抗真的是100欧姆,封装之后怎么就只有85欧姆了,我们去找包龙星问问。

仿真@包龙星:芯片使用了树脂填充0.5MM的外壳,封装基板表层的微带线的状态发生改变,应该用嵌入式微带线模型引入外壳材料参数计算阻抗,不同的外壳材料和外壳结构会不同程度的影响传输线的性能。不提前考虑外壳对阻抗的影响,封装填充之后阻抗恶化也不意外。

外壳的影响大致可以分以下三大类。

(1):GPU芯片、移动端的cpu等无外壳保护芯片,表层微带线阻抗不会有影响。

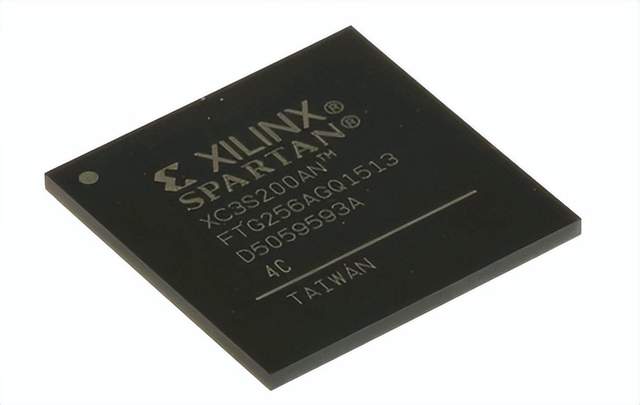

(2):保护DIE或金线的树脂外壳,应用十分广泛,大致模拟树脂填充的wost case情况是相比无外壳状态差分阻抗降低15欧姆左右。

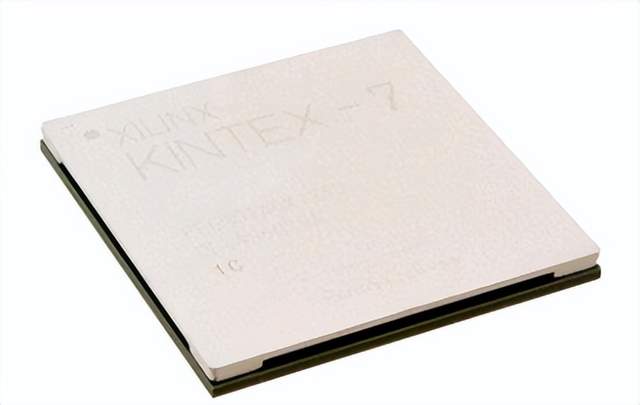

(3):保护DIE或金线并兼具散热的金属外壳。常见于桌面级、服务器级CPU芯片以及FPGA芯片等散热要求较高的芯片。大致模拟常规形制的金属外壳。wost case情况是相比无外壳状态差分阻抗降低2欧姆左右。

所以在设计和制板阶段就要考虑封装外壳对表层信号的影响:

1、根据填充材料属性和填充结构,提前模拟填充后的走线阻抗,获取外壳对阻抗的影响,设计和制板均需要加上这个影响,只有这样在芯片焊接和填充外壳之后的阻抗才会达到预期值。

2、使用金属外壳需要注意外壳粘接位置不要配置信号。如果是内置RF模块的芯片或者SIP不建议使用金属外壳。

每周一篇技术文章,学习更多内容,请百度搜索“一博科技官网”,直接进入学习

每周一篇技术文章,学习更多内容,请关注二维码

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网