日志

[ZZ]如何超出ADC采样带宽?妙招在手,轻松实现

| ||

在信号链中运用采样保持放大器(THA),可以从根本上扩展带宽,使其远远超出 ADC 采样带宽,满足苛刻高带宽的应用的需求。本文将证明,针对 RF 市场开发的最新转换器前增加一个 THA,便可实现超过 10 GHz 带宽。ps.本文定义的宽带是指使用大于数百MHz的信号带宽,其频率范围为 DC 附近至 5 GHz-10 GHz 区域。

打好基础

对于雷达、仪器仪表和通信应用,高GSPS转换器应用得非常广泛,因为它能提供更宽的频谱以扩展系统频率范围。然而,更宽的频谱对ADC本身的内部采样保持器提出了更多挑战,因为它通常未针对超宽带操作进行优化,而且ADC一般带宽有限,在这些更高模拟带宽区域中其高频线性度/SFDR会下降。

因此,在ADC前面使用单独的THA来拓展模拟带宽成为了一个理想的解决方案,如此便可在某一精确时刻对频率非常高的模拟/RF输入信号进行采样。该过程通过一个低抖动采样器实现信号采样,并在更宽带宽范围内降低了ADC的动态线性度要求,因为采样率RF模数转换过程中保持不变。

这种方案带来的好处显而易见:模拟输入带宽从根本上得以扩展,高频线性度显著改善,并且与单独的RF ADC性能相比,THA-ADC组件的高频SNR得到改进。

THA 特性及概述

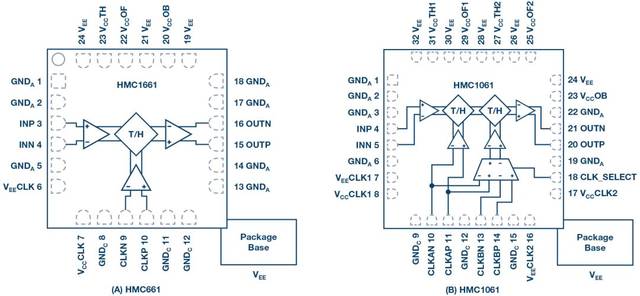

ADI 的 THA 系列产品可以在18 GHz带宽范围内提供精密信号采样,在DC至超过10 GHz的输入频率范围内具有9到10位线性度、1.05 mV噪声和<70 fs的随机孔径抖动性能。该器件可以4 GSPS工作,动态范围损失极小,具体型号包括HMC661 和 HMC1061。这些跟踪保持放大器可用于扩展高速模数转换和信号采集系统的带宽和/或高频线性度。

以单级THA HMC661为例,产生的输出由两段组成。在输出波形(正差分时钟电压)的采样模式间隔中,器件成为一个单位增益放大器,在输入带宽和输出放大器带宽的约束下,它将输入信号复制到输出级。在正时钟到负时钟跃迁时,器件以非常窄的采样时间孔径对输入信号采样,并且在负时钟间隔内,将输出保持在一个相对恒定的代表采样时刻信号的值。配合ADC进行前端采样时,常常优先使用单级器件(ADI 同时法布里了两级THA 的型号HMC1061),原因是多数高速ADC已经在内部集成一个THA,其带宽通常要小得多。因此,在ADC之前增加一个THA便构成一个复合双级组件(或一个三级组件,如果使用的是双级HMC1061),THA在转换器前面。采用同等技术和设计时,单级器件的线性度和噪声性能通常优于双级器件,原因是单级器件的级数更少。所以,单级器件常常是配合高速ADC进行前端采样的最佳选择。

图1. 采样保持拓扑结构:(1a) 单列,(1b) 双列

延迟映射 THA 和 ADC

开发采样保持器和ADC信号链的最困难任务之一,是在THA捕获采样事件的时刻与应将其移到ADC上以对该事件重新采样的时刻之间设置适当的时序延迟。设置两个高效采样系统之间的理想时间差的过程被称为延迟映射。

在电路板上完成该过程可能冗长乏味,因为纸面分析可能不会考虑PCB板上时钟走线传播间隔造成的相应延迟,内部器件组延迟,ADC孔径延迟,以及将时钟分为两个不同段所涉及到的相关电路(一条时钟走线用于THA,另一条时钟走线用于ADC)。设置THA和ADC之间延迟的一种方法是使用可变延迟线。这些器件可以是有源或无源的,目的是正确对准THA采样过程的时间并将其交给ADC进行采样。这保证了ADC对THA输出波形的稳定保持模式部分进行采样,从而准确表示输入信号。

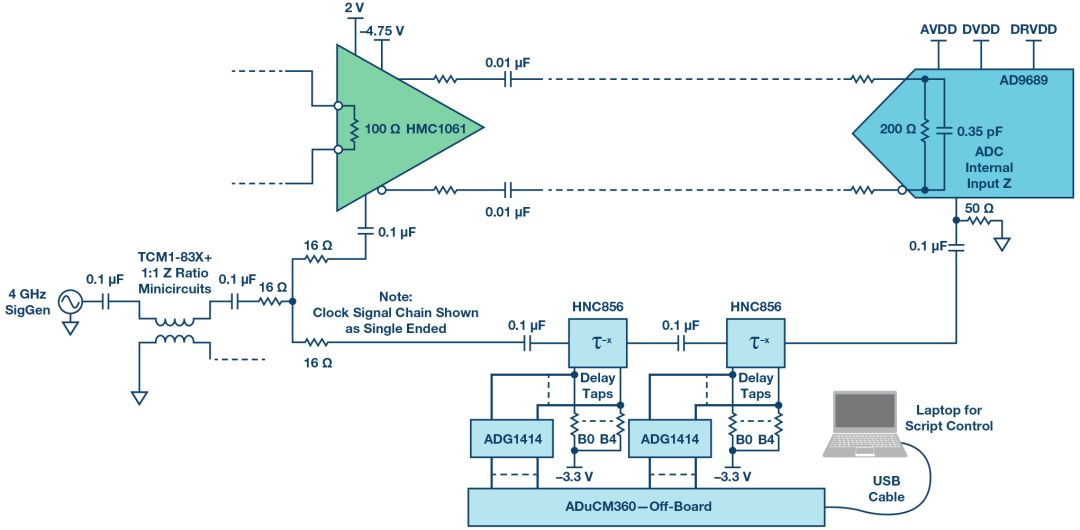

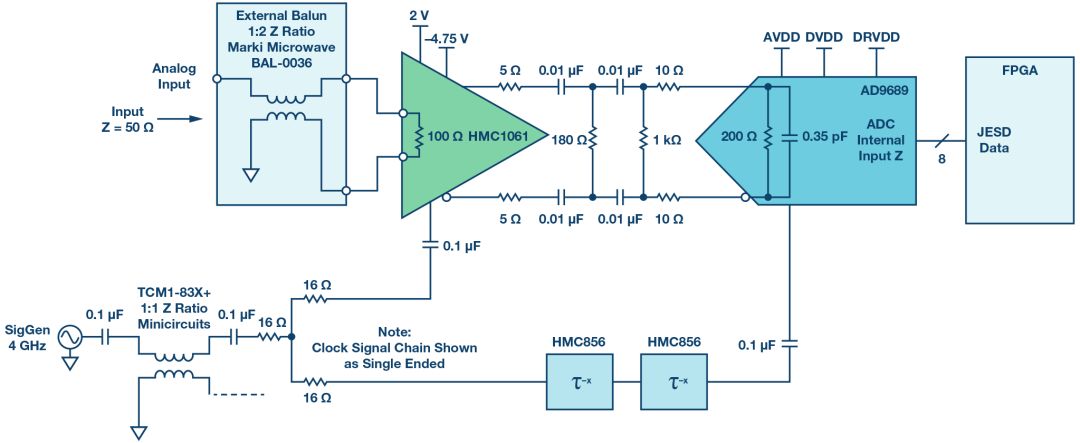

如图2所示, HMC856 可用来启动该延迟。它是一款5位QFN封装,90 ps的固有延迟,步进为3 ps或25ps ,32位的高速延时器。它的缺点是要设定/遍历每个延迟设置。要使能新的延迟设置,HMC856上的每个位/引脚都需要拉至负电压。因此,通过焊接下拉电阻在32种组合中找到最佳延迟设置会是一项繁琐的任务,为了解决这个问题,ADI使用串行控制的SPST开关和板外微处理器来帮助更快完成延迟设置过程。

图2. 延迟映射电路。

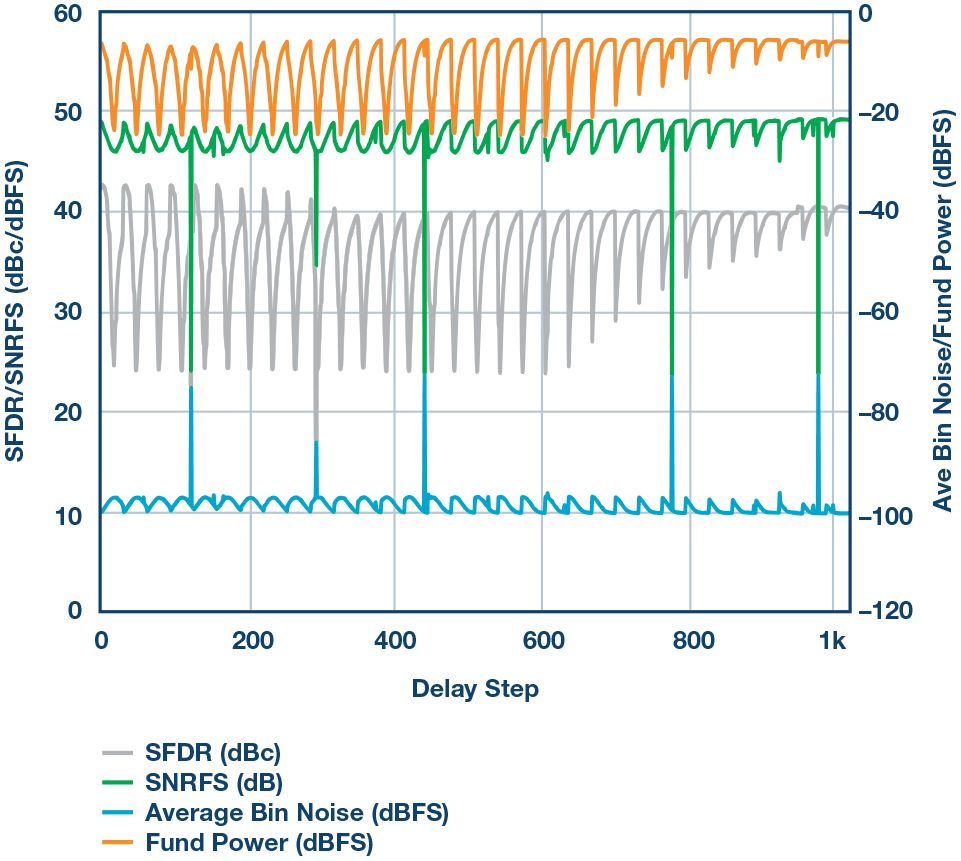

为了获得最佳延迟设置,将一个信号施加于THA和ADC组合,该信号应在ADC带宽范围之外。本例中,我们选择一个约10 GHz的信号,并施加-6 dBFS的电平(在FFT显示屏上捕获)。延迟设置现在以二 进制步进方式扫描,信号的电平和频率保持恒定。在扫描过程中显示并捕获FFT,收集每个延迟设置对应的基波功率和无杂散动态范围 (SFDR) 数值。

结果如图3a所示,基波功率、SFDR和SNR将随所应用的每个设置而变化。如图所示,当把采样位置放在更好的地方(THA将样本送至ADC的过程之中)时,基波功率将处于最高水平,而SFDR应处于最佳性能(即最低)。

图3a. 每个延迟设置上信号幅度和SFDR性能的映射结果。

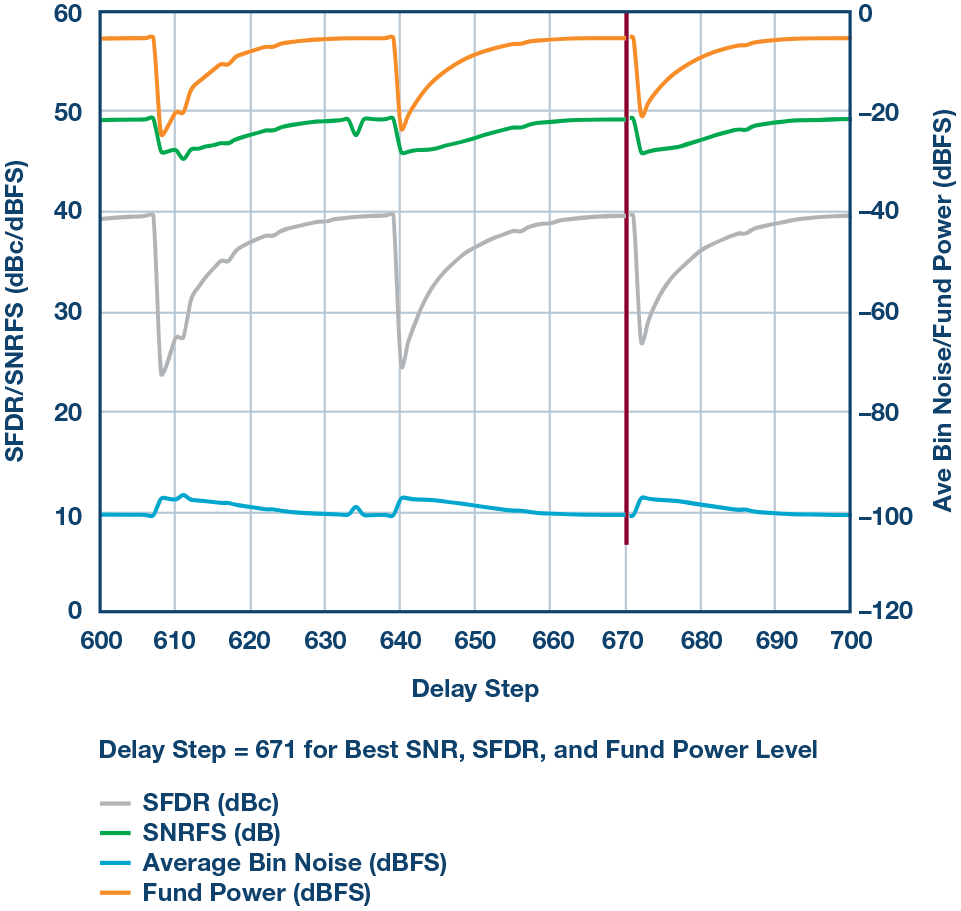

图3b为延迟映射扫描的放大视图,延迟设定点为671,即延迟应该保持固定于此窗口/位置。请记住,延迟映射程序仅对系统的相关采样频率有效,如果设计需要不同的采样时钟,则需要重新扫描。本例中,采样频率为4 GHz,这是该信号链中使用的THA器件的最高采样频率。

图3b. 每个延迟设置上信号幅度和SFDR性能的映射结果(放大)。

针对大量原始模拟带宽的前端设计

首先,如果应用的关键目标是处理10 GHz的带宽,我们显然应考虑RF方式。请注意,ADC仍然是电压型器件,不会考虑功率。这种情况下,"匹配"这个词应该谨慎使用。我们发现,让一个转换器前端在每个频率都与100 MSPS转换器匹配几乎是不可能的;高频率带宽的RF ADC不会有太大的不同,但挑战依旧。术语"匹配"应表示在前端设计中能产生最佳结果的优化。这是一个无所不包的术语,其中,输入阻抗、交流性能 (SNR/SFDR)、信号驱动强度或输入驱动、带宽以及通带平坦度,这些指标都能产生该特定应用的最佳结果。

最终,这些参数共同定义了系统应用的匹配性能。开始宽带前端设计时,布局可能是关键,同时应当最大限度地减少器件数量,以降低两个相邻IC之间的损耗。为了达到最佳性能,这两方面均非常重要。将模拟输入网络连接在一起时务必小心。走线长度以及匹配是最重要的,还应尽量减少过孔数量,如图4所示。

图4. THA和ADC布局。

信号通过差分模式连接到THA输入(我们同时是也提供单端射频信号输入的参考设计链路),形成单一前端网络。为了最大限度地减少过孔数量和总长度,我们在这里特别小心,让过孔不经过这两条模拟输入路径,并且帮助抵消走线连接中的任何线脚。

最终的设计相当简单,只需要注意几点,如图5所示。所使用的0.01 F电容是宽带类型,有助于在较宽频率范围内保持阻抗平坦。典型的成品型0.1 F电容无法提供平坦的阻抗响应,通常会在通带平坦度响应中引起较多纹波。THA输出端和ADC输入端的5和10串联电阻,有助于减少THA输出的峰化,并最大限度地降低ADC自身内部采样电容网络的残余电荷注入造成的失真。然而,这些值需要谨慎地选择,否则会增加信号衰减并迫使THA提高驱动强度,或者设计可能无法利用ADC的全部量程。

图5. THA和ADC前端网络及信号链。

最后讨论差分分流端接。当将两个或更多转换器连接在一起时,这点至关重要。通常,轻型负载(例如输入端有1 k负载)有助于保持线性并牵制混响频率。分流器的120 分流负载也有此作用,但会产生更多实际负载,本例中为50 ,这正是THA希望看到并进行优化的负载。

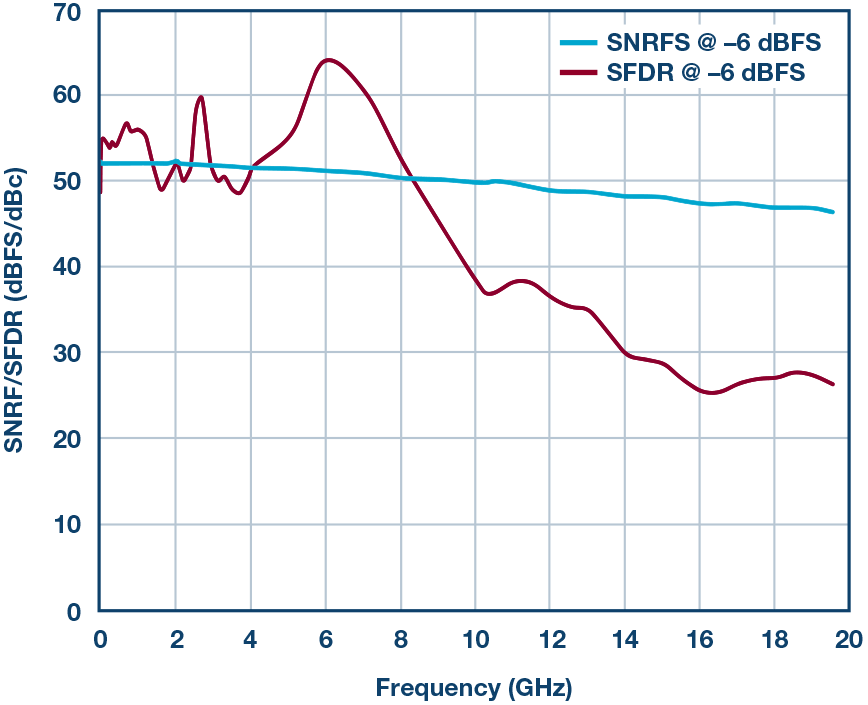

现在看结果!检查图6中的信噪比或SNR,可以看出在15 GHz范围上可以实现8位的ENOB(有效位数)。这是相当不错的,想想对于相同性能的13 GHz示波器,您可能支付了12万美元。当频率向L、S、C和X波段移动时,集成带宽(即噪声)和抖动限制开始变得显著,因此我们看到性能出现滚降。

图6. –6 dBFS时的SNRFS/SFDR性能结果。

还应注意,为了保持THA和ADC之间的电平恒定,ADC的满量程输入通过SPI寄存器内部更改为1.0 V p-p。这有助于将THA保持在线性区域内,因为其最大输出为1.0 V p-p差分。

同时显示了线性度结果或SFRD。这里,到8 GHz为止的线性度超过50 dBc,到10 GHz为止的线性度超过40 dBc。为在如此宽的频率范围上达到最佳线性度,此处的设计利用 AD9689模拟输入缓冲电流设置特性进行了优化(通过SPI控制寄存器)。

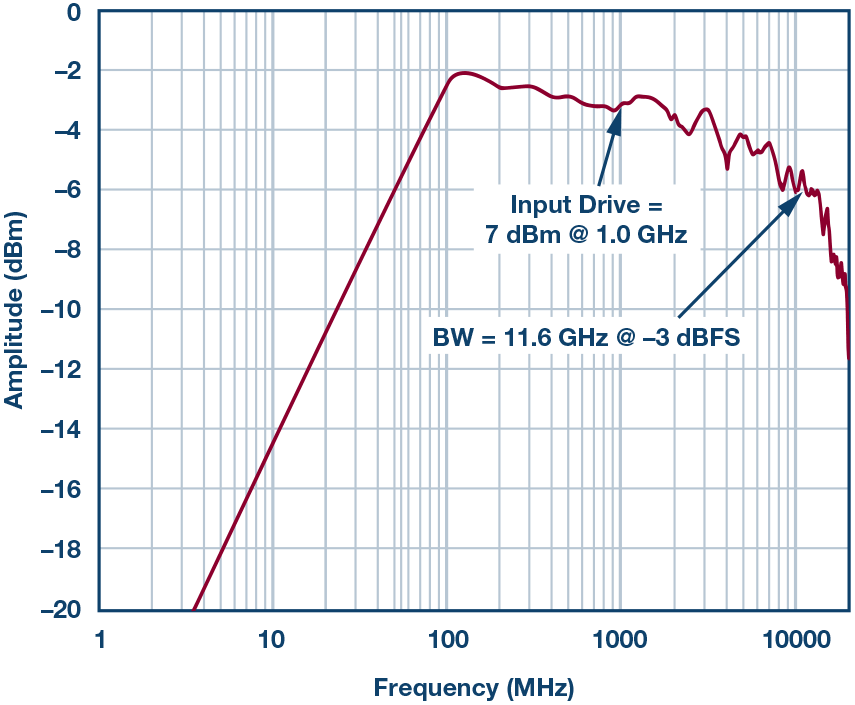

图7显示了通带平坦度,证明在RF ADC之前增加一个THA可以实现 10 GHz的带宽,从而充分扩展AD9689的模拟带宽。

图7. THA和ADC网络及信号链—带宽结果。

结语

对于那些需要在多GHz模拟带宽上实现最佳性能的应用,THA几乎是必不可少的,至少目前是如此!RF ADC正在迅速赶上。很容易明白,在对较宽带宽进行采样以覆盖多个目标频带时,GSPS转换器在理论上具有易用性优势,可以消除前端RF带上的一个或多个向下混频级。但是,实现更高范围的带宽可能会带来设计挑战和维护问题。

在系统中使用THA时,应确保采样点的位置在THA和ADC之间进行了优化。使用本文所述的延迟映射程序将产生总体上最佳的性能结果。了解程序是乏味的,但是非常重要。最后应记住,匹配前端实际上意味在应用的给定一组性能需求下实现最佳性能。在X波段频率进行采样时,乐高式方法(简单地将50 阻抗模块连接在一起)可能不是最好的方法。

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网