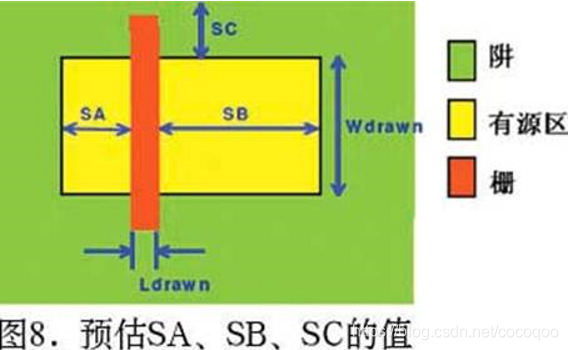

预先放大或缩小MOS管。PMOS管的电流随SA/SB的增大而变小,所以可以预先放大PMOS管;NMOS管的电流随SA/SB的增大而增大,所以可以预先缩小NMOS管。

这种作用类似于方法一,都是将WPE和STI效应在电路设计阶段就考虑进来,而不是等到版图完成之后才能调整。但这种方法对于比较有经验的设计者或者有实验数据的设计者来说才比较适用。

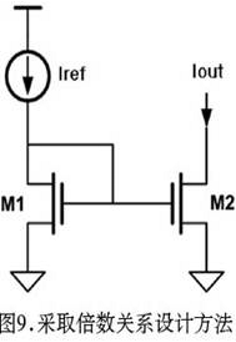

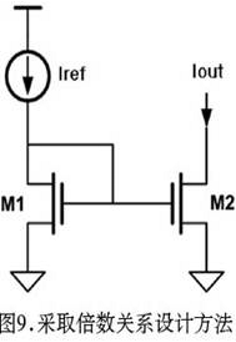

对于对称性要求比较高的电路(如电流镜、差分放大等),设计者应该尽量采取整数倍的设计方法,采用同样长度的管子,管子宽度的设计也尽量用倍数的关系。这种方法有助于提高管子制造出来之后的对称性。

理论上,这种电路可以精确的复制电流而不受工艺和温度的影响,Iout与Iref的比值有器件尺寸的比率决定,但是实际上,管子之间的比率与WPE和STI效应息息相关。所以如选择M1管子为子单元,M2管子应为子单元的整数倍为好,在电路前期仿真阶段可以看到这种方法的优越性。

方法四:

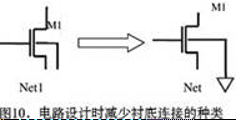

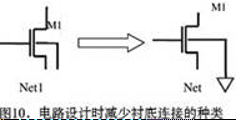

在不影响电路设计性能的情况下,尽量将PMOS管衬底连接电源,NMOS管衬底连接地,而不要到中间电平,可以减少阱的个数。 如图10所示,从电路设计阶段就减少衬底连接种类,有利于在版图设计时减少阱的个数,进而直接降低WPE以及STI对MOS管影响。

在上图中,在设计规格满足的情况下,我们应该尽量采用将M1管的衬底连接到VSS,而不是连接到NET1的方法来进行设计,这样有助于在版图的布局优化。

方法五:

在电路设计后期,即版图设计完成之后,进行版图寄生参数的提取,然后再进行电路仿真,即我们常说的后仿。

用HSPICE做电路仿真时,传统的BSIM3 SPICE Model并没有把WPE/STI效应估算进去,而BSIM4 Spice Model开始支持这些效应了,所以要仿真使用BSIM4的模型。目前,晶圆厂的先进制成都已经提供了这种模型给用户使用了。这种方法可以进行最为准确的设计,但是如果后仿之后才考虑所有版图因素的话,这样会造成设计循环次数较多。

前四种办法在版图设计没有完成时采用,可以有效地缩短设计周期,减少设计的循环次数。第五种方法,对于考虑WPE/STI效应更有效,但会需要较长的设计周期。随着工艺的越来越先进,后期仿真又是必不可少的,特别是对于精确的设计。

版图设计中如何减小STI、WPE的影响

版图设计是创建工程制图的精确的物理描述的过程,而这一物理描述遵守有制造工艺、设计流程以及通过仿真显示为可行的性能要求所带来的一系列约束[6]。版图设计之后得到的GDSII格式的数据将交给掩模厂进行掩模的制作,以至最终送到晶圆厂(代工厂)生产线上去做芯片的生产制造。所以可以说版图的设计与生产制造出来的芯片的有更为直接的关系,因而在版图设计阶段考虑制造工艺的影响至关重要。那么,版图设计中如何减小STI、WPE的影响呢?下面针对STI、WPE的影响提出了几个IP模块版图设计的要点:

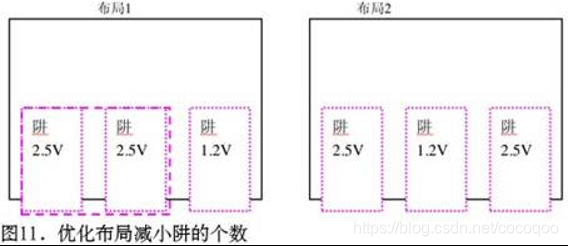

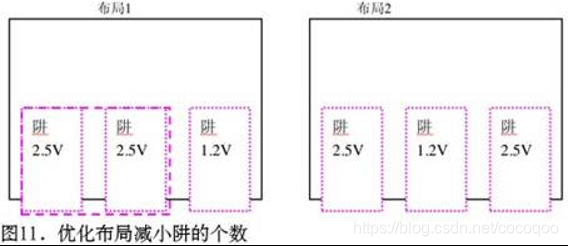

在版图布局规划阶段,优化阱的布局以减小阱的个数,比如将同一电位的器件放在一个阱里面,这样可以减小或避免WPE效应(图11)。

可以看出布局1比布局2有优势,因为相同的2.5V的阱可以进行合并,进而形成一个大的阱,受阱边界影响的MOS管的个数就会减少,WPE效应降低了,甚至几乎没有什么影响了。

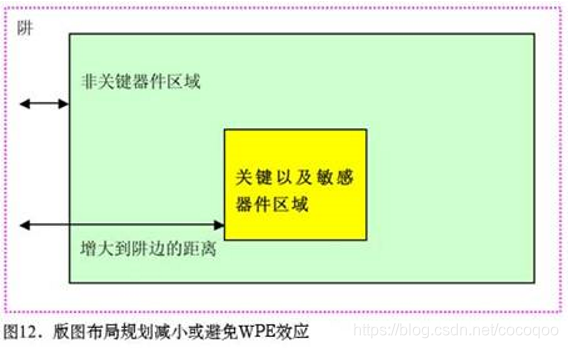

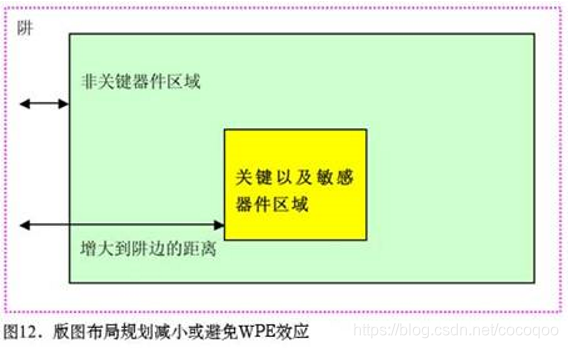

注意关键器件的布局,尽量将关键器件放置在离阱的边界比较远的地方,这样可以减小或避免WPE效应(图12)。

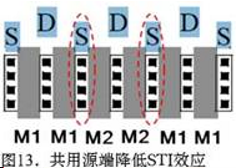

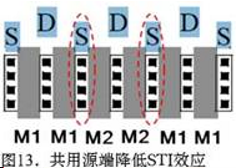

提高MOS管源、漏两端的可共用性,这样可以降低STI效应。如图13所示,将MOS管M1和M2实现源端的共用。

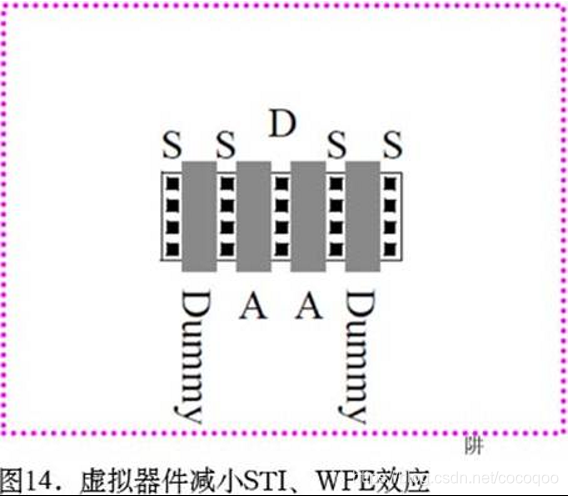

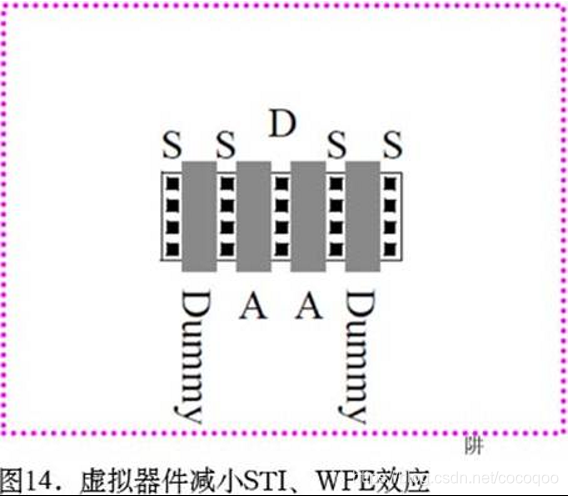

在有限的空间下,多加一些虚拟器件(Dummy device),这样就可以使关键器件远离阱的边缘,减小WPE;又可以增大MOS管源、漏两端的面积,从而降低STI效应(图14)。

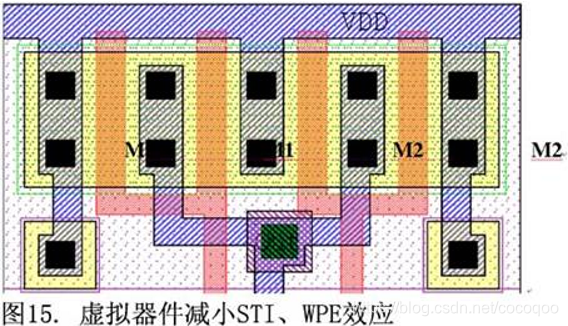

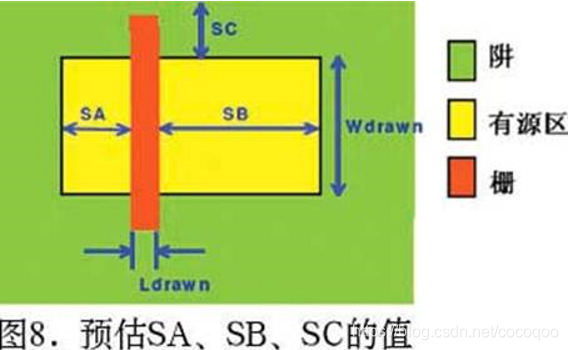

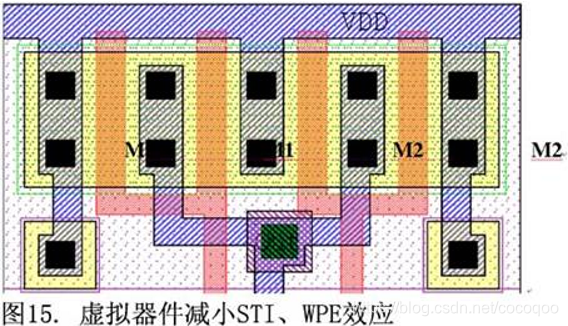

对于对称性要求比较高的电路(如电流镜、差分放大等),设计者应该尽量采取单元模块调用的设计方法。先作一个单元模块具有一定长度和宽度的管子,其它的管子都以这单元模块为单元进行重复调用,组成新的管子。这样,这些管子之间就会具有类似的特性,如SA、SB(STI效应)或者SC(WPE效应)的值。进行调用构建新的管子M1、M2,可以看出M1和M2具有类似的SA、SB、SC值(图15)。

总结

STI、WPE是在深亚微米制造工艺时必须考虑的因素,特别是纳米级的制造工艺对器件有越来越重要的影响。如果不加以考虑,芯片会面临性能无法提高的影响,以至于会导致芯片无法工作。而在电路设计和版图设计中就融入这些因素,可以有效地缩短产品周期,降低生产成本。然而越来越多的工艺制作因素影响着IP模块的设计,这对于IP模块设计来说,更多的了解工艺变得非常重要。

————————————————

版权声明:本文为CSDN博主「luobingyin」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/cocoqoo/article/details/92639159

/2

/2